# Information technology —

Telecommunications and information exchange between systems— Local and metropolitan area networks—Specific requirements—

# Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) access method and physical layer specifications

SECTION THREE: This section includes Clauses 34 through 43 and Annexes 36A through 43C.

#### 34. Introduction to 1000 Mb/s baseband network

#### 34.1 Overview

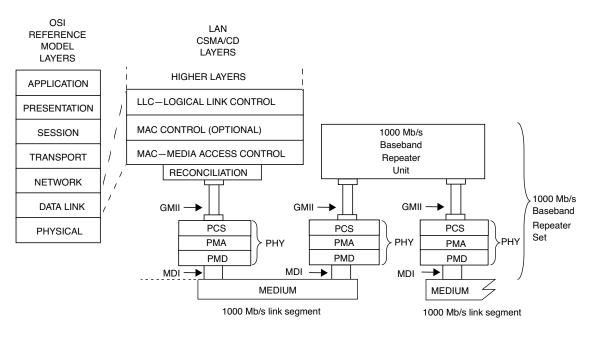

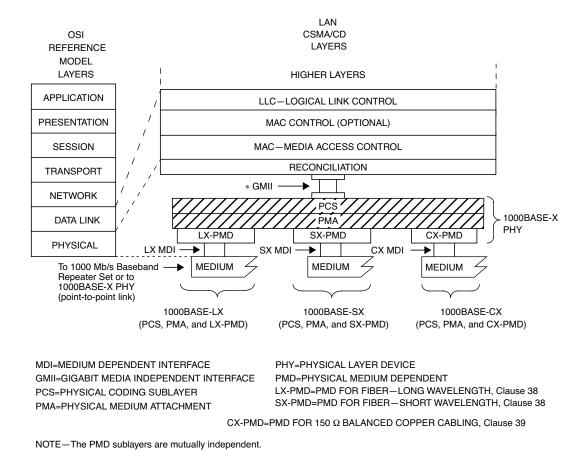

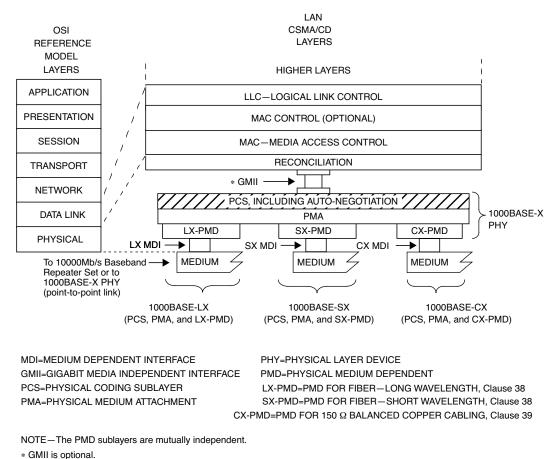

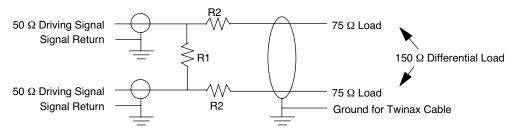

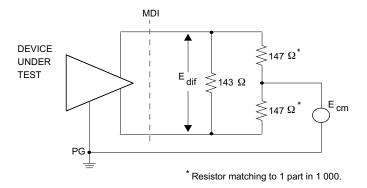

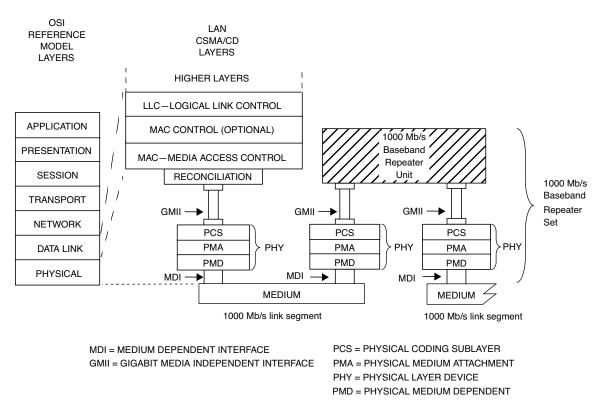

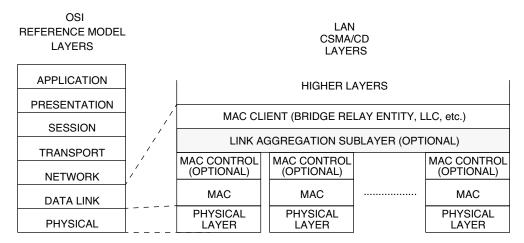

Gigabit Ethernet couples an extended version of the ISO/IEC 8802-3 (CSMA/CD MAC) to a family of 1000 Mb/s Physical Layers. The relationships among Gigabit Ethernet, the extended ISO/IEC 8802-3 (CSMA/CD MAC), and the ISO/IEC Open System Interconnection (OSI) reference model are shown in Figure 34–1.

Gigabit Ethernet uses the extended ISO/IEC 8802-3 MAC layer interface, connected through a Gigabit Media Independent Interface layer to Physical Layer entities (PHY sublayers) such as 1000BASE-LX, 1000BASE-SX, and 1000BASE-CX, and 1000BASE-T.

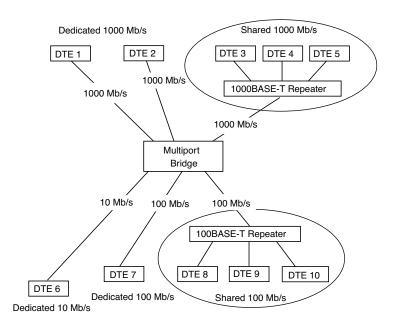

Gigabit Ethernet extends the ISO/IEC 8802-3 MAC beyond 100 Mb/s to 1000 Mb/s. The bit rate is faster, and the bit times are shorter—both in proportion to the change in bandwidth. In full duplex mode, the minimum packet transmission time has been reduced by a factor of ten. Achievable topologies for 1000 Mb/s full duplex operation are comparable to those found in 100BASE-T full duplex mode. In half duplex mode, the minimum packet transmission time has been reduced, but not by a factor of ten. Cable delay budgets are similar to those in 100BASE-T. The resulting achievable topologies for the half duplex 1000 Mb/s CSMA/CD MAC are similar to those found in half duplex 100BASE-T.

#### 34.1.1 Reconciliation Sublayer (RS) and Gigabit Media Independent Interface (GMII)

The Gigabit Media Independent Interface (Clause 35) provides an interconnection between the Media Access Control (MAC) sublayer and Physical Layer entities (PHY) and between PHY Layer and Station Management (STA) entities. This GMII supports 1000 Mb/s operation through its eight bit wide (octet wide) transmit and receive paths. The Reconciliation sublayer provides a mapping between the signals provided at the GMII and the MAC/PLS service definition.

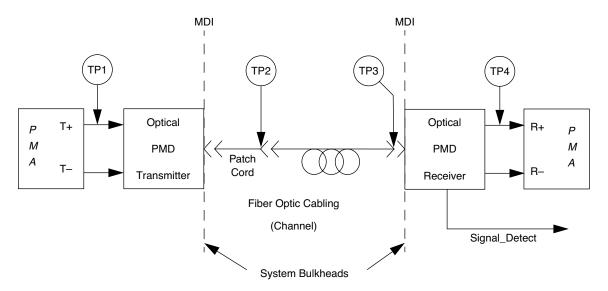

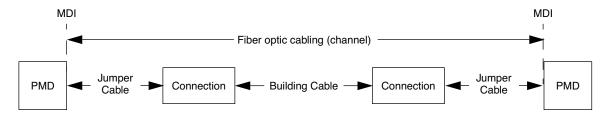

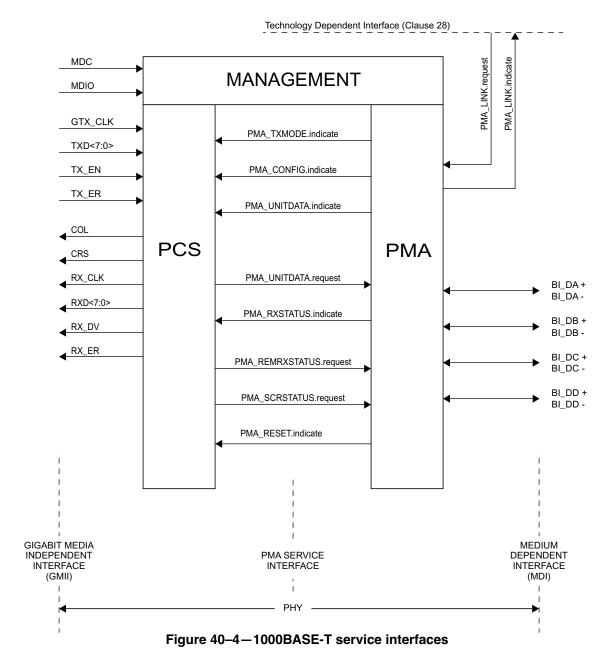

MDI = MEDIUM DEPENDENT INTERFACE GMII = GIGABIT MEDIA INDEPENDENT INTERFACE PCS = PHYSICAL CODING SUBLAYER

PMA = PHYSICAL MEDIUM ATTACHMENT

PHY = PHYSICAL LAYER DEVICE

PMD = PHYSICAL MEDIUM DEPENDENT

Figure 34-1 - Architectural positioning of Gigabit Ethernet (1000 Mb/s operation)

#### 34.1.2 Physical Layer signaling systems

This standard specifies a family of Physical Layer implementations. The generic term 1000 Mb/s MAC refers to any use of the 1000 Mb/s ISO/IEC 8802-3 CSMA/CD MAC (the Gigabit Ethernet MAC) coupled with any physical layer implementation.

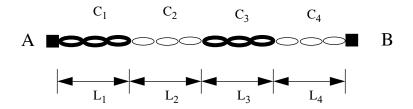

The term 1000BASE-X refers to a specific family of physical layer implementations specified in Clauses 36–39. The 1000BASE-X family of physical layer standards has been adapted from the ANSI X3.230-1994 [B20] (Fibre Channel) FC-0 and FC-1 physical layer specifications and the associated 8B/10B data coding method. The 1000BASE-X family of physical layer implementations is composed of 1000BASE-SX, 1000BASE-LX, and 1000BASE-CX.

All 1000BASE-X PHY devices share the use of common PCS, PMA, and Auto-Negotiation specifications (see Clauses 36 and 37). The 1000BASE-T PHY (Clause 40) uses four pairs of Category 5 balanced copper cabling. Clause 40 defines its own PCS, which does not use 8B/10B coding.

Specifications unique to the physical operation of each physical layer device are shown in the following table:

| 1000BASE-SX Short Wave Length<br>Optical | Duplex multimode fibers                                                              | Clause 38 |

|------------------------------------------|--------------------------------------------------------------------------------------|-----------|

| 1000BASE-LX Long Wave Length<br>Optical  | Duplex single-mode fibers or<br>Duplex multimode fibers                              | Clause 38 |

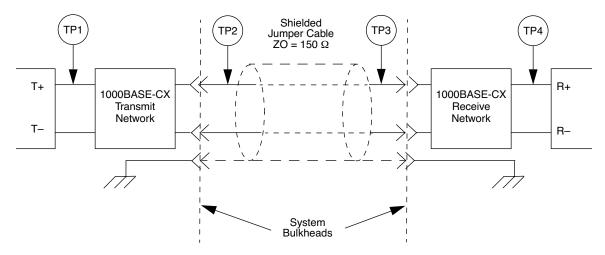

| 1000BASE-CX Shielded Jumper<br>Cable     | Two pairs of specialized balanced cabling                                            | Clause 39 |

| 1000BASE-T Category 5 UTP                | Advanced multilevel signaling over four pairs of Category 5 balanced copper cabling. | Clause 40 |

#### 34.1.3 Repeater

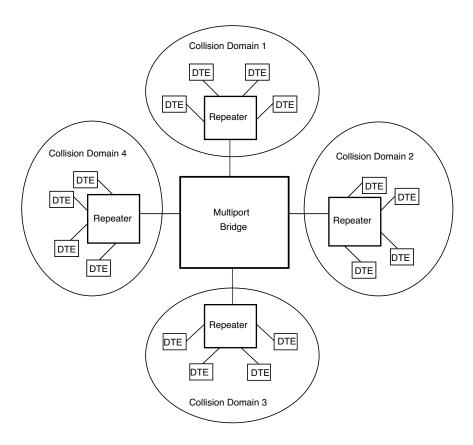

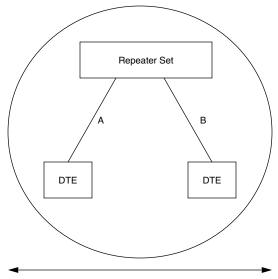

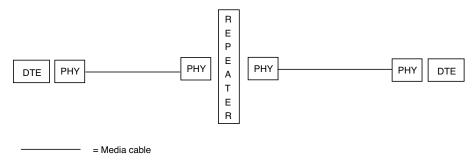

A repeater set (Clause 41) is an integral part of any Gigabit Ethernet network with more than two DTEs in a collision domain. A repeater set extends the physical system topology by coupling two or more segments. Only one repeater is permitted within a single collision domain.

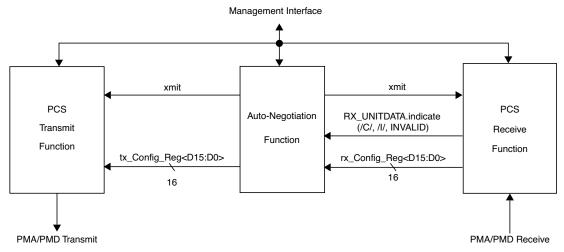

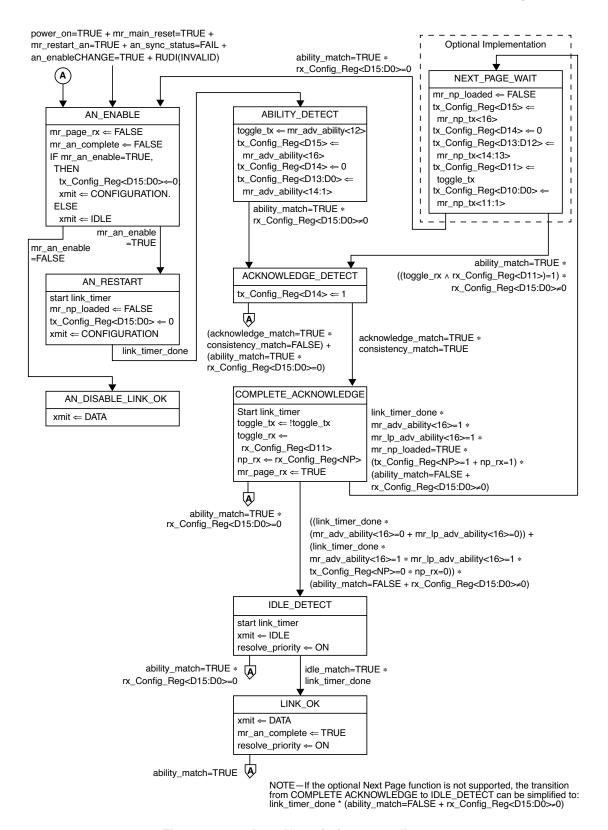

#### 34.1.4 Auto-Negotiation, type 1000BASE-X

Auto-Negotiation (Clause 37) provides a 1000BASE-X device with the capability to detect the abilities (modes of operation) supported by the device at the other end of a link segment, determine common abilities, and configure for joint operation. Auto-Negotiation is performed upon link startup through the use of a special sequence of reserved link code words. Clause 37 adopts the basic architecture and algorithms from Clause 28, but not the use of fast link pulses.

#### 34.1.5 Physical Layer line signaling for 10 Mb/s and 100 Mb/s Auto-Negotiation on twisted pair

Auto-Negotiation (Clause 28) is used by 1000BASE-T devices to detect the abilities (modes of operation) supported by the device at the other end of a link segment, determine common abilities, and configure for joint operation. Auto-Negotiation is performed upon link startup through the use of a special sequence of fast link pulses.

#### 34.1.6 Management

Managed objects, attributes, and actions are defined for all Gigabit Ethernet components (Clause 30). That clause consolidates all IEEE 802.3<sup>®</sup> management specifications so that 10/100/1000 Mb/s agents can be managed by existing network management stations with little or no modification to the agent code.

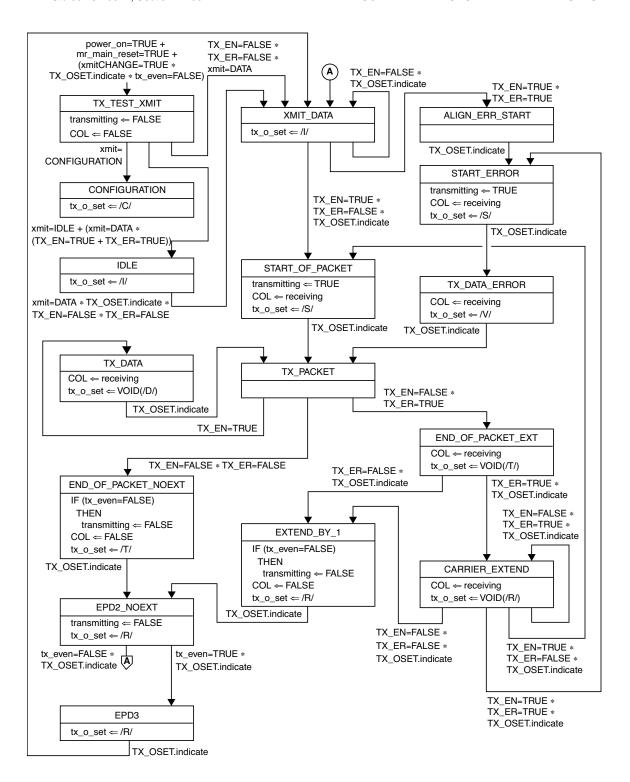

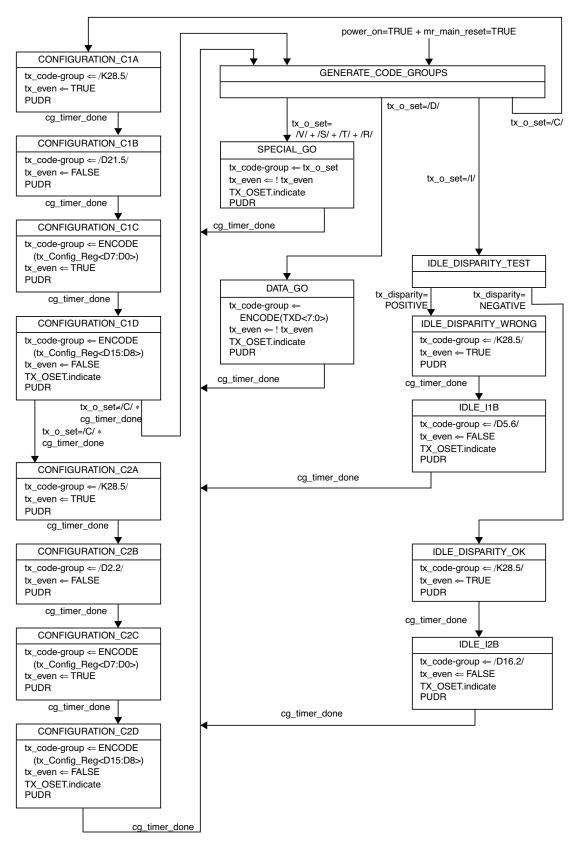

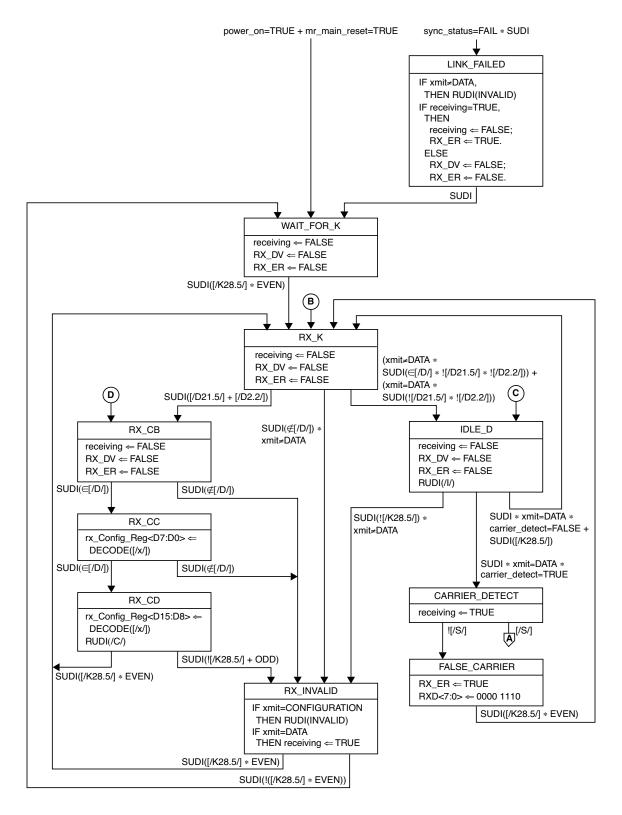

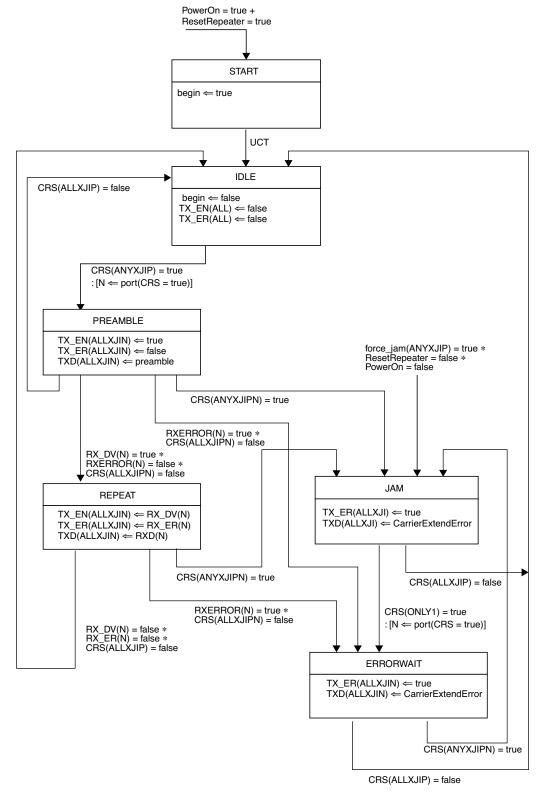

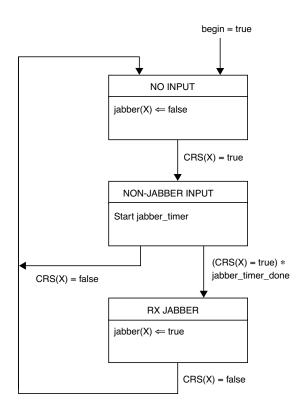

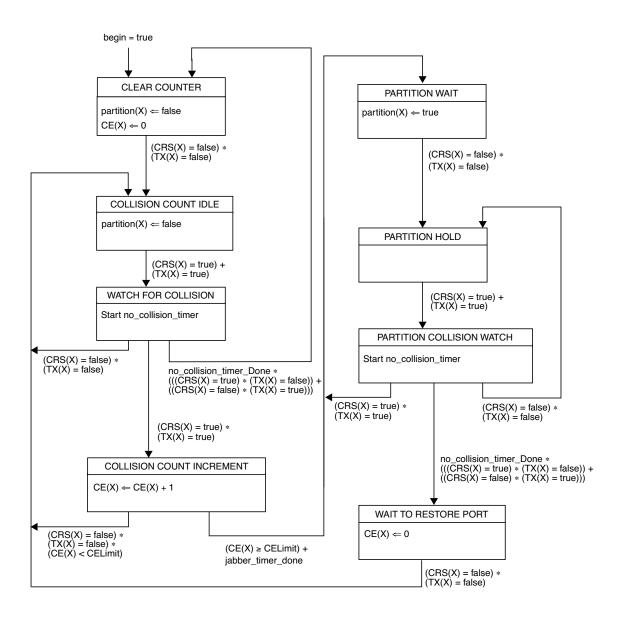

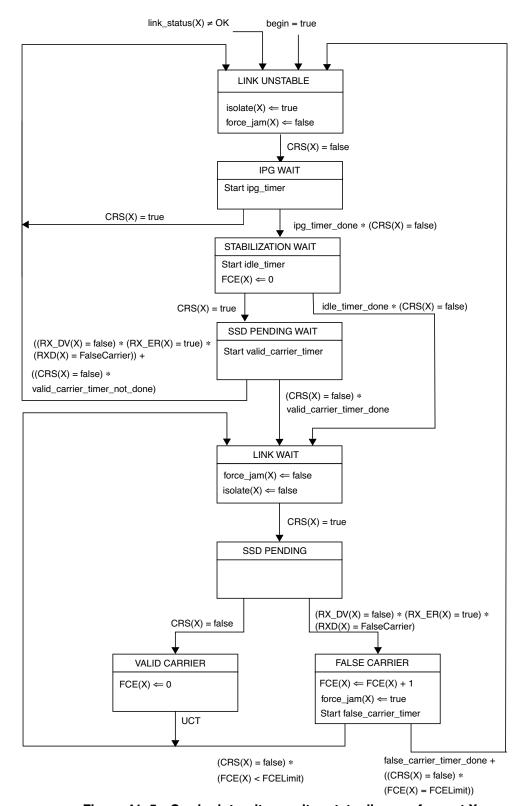

#### 34.2 State diagrams

State machine diagrams take precedence over text.

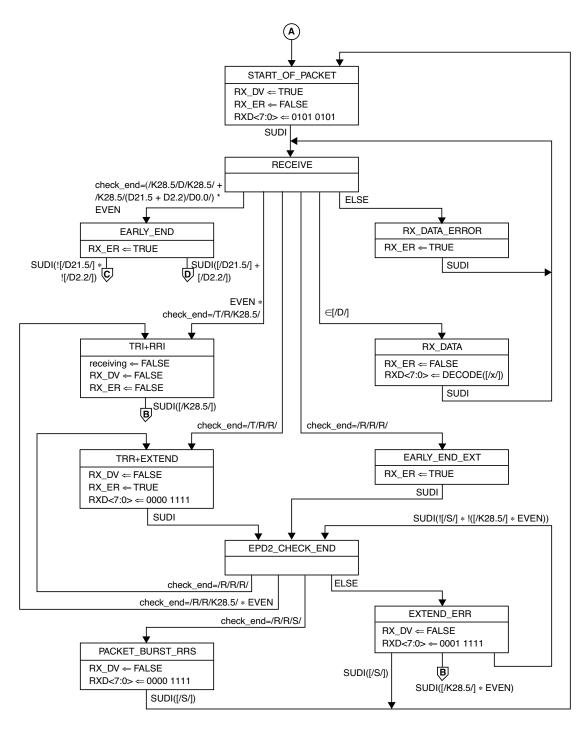

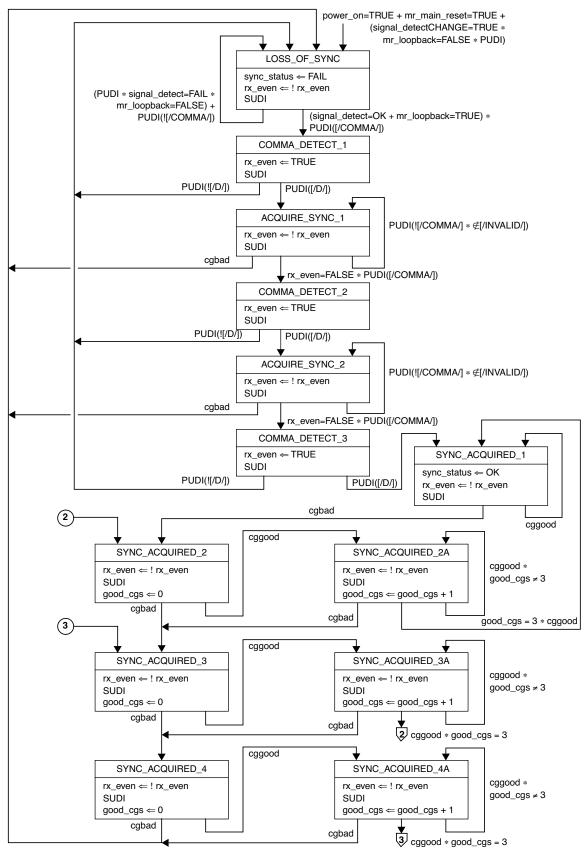

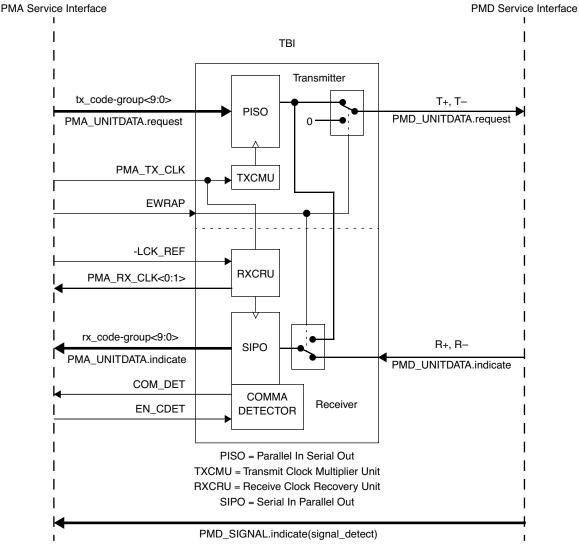

The conventions of 1.2 are adopted, along with the extensions listed in 21.5.

#### 34.3 Protocol Implementation Conformance Statement (PICS) proforma

The supplier of a protocol implementation that is claimed to conform to any part of IEEE 802.3<sup>®</sup>, Clauses 35 through 41, shall complete a Protocol Implementation Conformance Statement (PICS) proforma.

A completed PICS proforma is the PICS for the implementation in question. The PICS is a statement of which capabilities and options of the protocol have been implemented. A PICS is included at the end of each clause as appropriate. Each of the Gigabit Ethernet PICS conforms to the same notation and conventions used in 100BASE-T (see 21.6).

## 34.4 Relation of Gigabit Ethernet to other standards

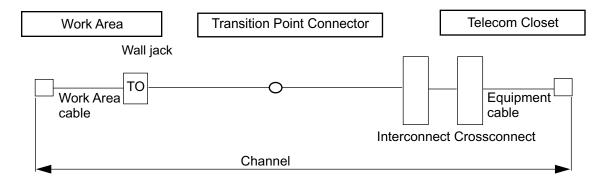

Suitable entries for Table G1 of ISO/IEC 11801: 1995, annex G, would be as follows:

a) Within the section Optical Link:

CSMA/CD 1000BASE-SX ISO/IEC 8802-3/ PDAM 26

b) Within the section Optical Link:

CSMA/CD 1000BASE-LX ISO/IEC 8802-3/PDAM 26

c) Within the section Balanced Cabling Link Class D (defined up to 100MHz):

CSMA/CD 1000BASE-T\* ISO/IEC8802-3/DAD 1995

A suitable entry for Table G5 of ISO/IEC 11801: 1995, Annex G, would be as follows:

Table 34-1-Table G5 of ISO/IEC 11801

|                        |                           | Fibre                   |                         |                           | Optical link per 6      |                         |                           |                         |                         |                           |                         |                         |

|------------------------|---------------------------|-------------------------|-------------------------|---------------------------|-------------------------|-------------------------|---------------------------|-------------------------|-------------------------|---------------------------|-------------------------|-------------------------|

|                        | per Cl                    | per Clauses 5, 7, and 8 |                         | Н                         | lorizont                | al                      | Building backbone         |                         |                         | Campus backbone           |                         |                         |

|                        | 62.5/<br>125<br>μm<br>ΜΜF | 50/<br>125<br>μm<br>ΜΜF | 10/<br>125<br>μm<br>SMF | 62.5<br>/125<br>μm<br>ΜΜF | 50/<br>125<br>μm<br>ΜΜF | 10/<br>125<br>μm<br>SMF | 62.5<br>/125<br>μm<br>ΜΜF | 50/<br>125<br>μm<br>ΜΜF | 10/<br>125<br>μm<br>SMF | 62.5<br>/125<br>μm<br>ΜΜF | 50/<br>125<br>μm<br>ΜΜF | 10/<br>125<br>μm<br>SMF |

| 8802-3:<br>1000BASE-SX | Ι                         | I                       |                         | N                         | N                       |                         | Ι                         | N                       |                         | Ι                         | I                       |                         |

| 8802-3:<br>1000BASE-LX | Ι                         | I                       | I                       | N                         | N                       | N                       | N                         | N                       | N                       | I                         | I                       | N                       |

NOTE—"N" denotes normative support of the media in the standard.

Suitable entries for table G4 of ISO/IEC 11801:1995 Annex G would be:

Table 34-2-Table G4 of ISO/IEC 11801:1995

|                    |                                 | Balanced cabling                |                |                                 |                                 |                                 | Pe               | erformance based cabling per 6 |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

|--------------------|---------------------------------|---------------------------------|----------------|---------------------------------|---------------------------------|---------------------------------|------------------|--------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

|                    |                                 | per                             | Clau           | ses 5                           | , 7, a                          | nd 8                            |                  | (                              | Class            | A                | (                | Class            | В                | 0                | Class            | C                | C                | lass ]           | D                |

|                    | C<br>a<br>t<br>3<br>1<br>0<br>Ω | C<br>a<br>t<br>4<br>1<br>0<br>0 | C at 5 1 0 Ω   | C<br>a<br>t<br>3<br>1<br>2<br>0 | C<br>a<br>t<br>4<br>1<br>2<br>0 | C<br>a<br>t<br>5<br>1<br>2<br>0 | 1<br>5<br>0<br>Ω | 1<br>0<br>0<br>Ω               | 1<br>2<br>0<br>Ω | 1<br>5<br>0<br>Ω | 1<br>0<br>0<br>Ω | 1<br>2<br>0<br>Ω | 1<br>5<br>0<br>Ω | 1<br>0<br>0<br>Ω | 1<br>2<br>0<br>Ω | 1<br>5<br>0<br>Ω | 1<br>0<br>0<br>Ω | 1<br>2<br>0<br>Ω | 1<br>5<br>0<br>Ω |

| 8802-3: 1000BASE-T |                                 |                                 | I <sup>a</sup> |                                 |                                 |                                 |                  |                                |                  |                  |                  |                  |                  |                  |                  |                  | I <sup>a</sup>   |                  |                  |

NOTE—"I" denotes that there is information in the International Standard regarding operation on this media.

<sup>\*</sup>To support 1000BASE-T applications, Class D links shall meet the requirements for return loss, ELFEXT and MDELFEXT specified in 40.7.

<sup>&</sup>quot;I" denotes that there is information in the International Standard regarding operation on this media.

<sup>&</sup>lt;sup>a</sup>8802-3 imposes additional requirements on return loss, ELFEXT and MDELFEXT.

# 35. Reconciliation Sublayer (RS) and Gigabit Media Independent Interface (GMII)

#### 35.1 Overview

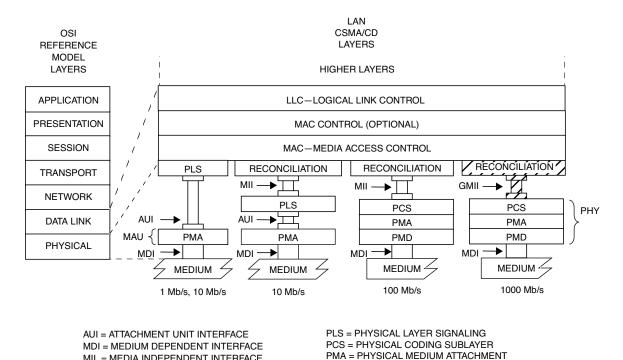

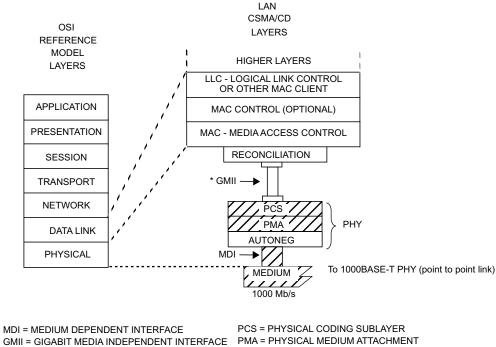

This clause defines the logical and electrical characteristics for the Reconciliation Sublayer (RS) and Gigabit Media Independent Interface (GMII) between CSMA/CD media access controllers and various PHYs. Figure 35-1 shows the relationship of the Reconciliation sublayer and GMII to the ISO/IEC OSI reference model.

Figure 35-1-GMII location in the OSI protocol stack

PHY = PHYSICAL LAYER DEVICE

PMD = PHYSICAL MEDIUM DEPENDENT

The purpose of this interface is to provide a simple, inexpensive, and easy-to-implement interconnection between Media Access Control (MAC) sublayer and PHYs, and between PHYs and Station Management (STA) entities.

This interface has the following characteristics:

It is capable of supporting 1000 Mb/s operation.

MII = MEDIA INDEPENDENT INTERFACE

MAU = MEDIUM ATTACHMENT UNIT

GMII = GIGABIT MEDIA INDEPENDENT INTERFACE

- b) Data and delimiters are synchronous to clock references.

- c) It provides independent eight-bit-wide transmit and receive data paths.

- It provides a simple management interface.

- It uses signal levels, compatible with common CMOS digital ASIC processes and some bipolar e) processes.

- f) It provides for full duplex operation.

#### 35.1.1 Summary of major concepts

- a) The GMII is based on the MII defined in Clause 22.

- b) Each direction of data transfer is serviced by Data (an eight-bit bundle), Delimiter, Error, and Clock signals.

- c) Two media status signals are provided. One indicates the presence of carrier, and the other indicates the occurrence of a collision.

- d) The GMII uses the MII management interface composed of two signals that provide access to management parameters and services as specified in Clause 22.

- e) MII signal names have been retained and the functions of most signals are the same, but additional valid combinations of signals have been defined for 1000 Mb/s operation.

- f) The Reconciliation sublayer maps the signal set provided at the GMII to the PLS service primitives provided to the MAC.

- g) GMII signals are defined such that an implementation may multiplex most GMII signals with the similar PMA service interface defined in Clause 36.

#### 35.1.2 Application

This clause applies to the interface between the MAC and PHYs, and between PHYs and Station Management entities. The implementation of the interface is primarily intended as a chip-to-chip (integrated circuit to integrated circuit) interface implemented with traces on a printed circuit board. A motherboard-to-daughterboard interface between two or more printed circuit boards is not precluded.

This interface is used to provide media independence so that an identical media access controller may be used with any of the copper and optical PHY types.

#### 35.1.3 Rate of operation

The GMII supports only 1000 Mb/s operation and is defined within this clause. Operation at 10 Mb/s and 100 Mb/s is supported by the MII defined in Clause 22.

PHYs that provide a GMII shall support 1000 Mb/s operation, and may support additional rates using other interfaces (e.g., MII). PHYs must report the rates at which they are capable of operating via the management interface, as described in 22.2.4. Reconciliation sublayers that provide a GMII shall support 1000 Mb/s and may support additional rates using other interfaces.

#### 35.1.4 Allocation of functions

The allocation of functions at the GMII balances the need for media independence with the need for a simple and cost-effective interface.

While the Attachment Unit Interface (AUI) was defined to exist between the Physical Signaling (PLS) and Physical Medium Attachment (PMA) sublayers for 10 Mb/s DTEs, the GMII (like the Clause 22 MII) maximizes media independence by cleanly separating the Data Link and Physical Layers of the ISO/IEC seven-layer reference model. This allocation also recognizes that implementations can benefit from a close coupling between the PLS or PCS sublayer and the PMA sublayer.

#### 35.2 Functional specifications

The GMII is designed to make the differences among the various media transparent to the MAC sublayer. The selection of logical control signals and the functional procedures are all designed to this end.

#### 35.2.1 Mapping of GMII signals to PLS service primitives and Station Management

The Reconciliation sublayer maps the signals provided at the GMII to the PLS service primitives defined in Clause 6. The PLS service primitives provided by the Reconciliation sublayer, and described here, behave in exactly the same manner as defined in Clause 6.

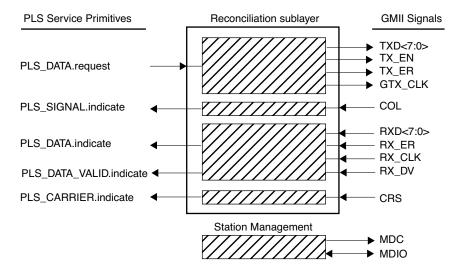

Figure 35–2 depicts a schematic view of the Reconciliation sublayer inputs and outputs, and demonstrates that the GMII management interface is controlled by the Station Management entity (STA).

Figure 35–2—Reconciliation Sublayer (RS) inputs and outputs and STA connections to GMII

#### 35.2.1.1 Mapping of PLS\_DATA.request

#### 35.2.1.1.1 Function

Map the primitive PLS\_DATA.request to the GMII signals TXD<7:0>, TX\_EN, TX\_ER and GTX\_CLK.

#### 35.2.1.1.2 Semantics of the service primitive

PLS DATA.request (OUTPUT UNIT)

The OUTPUT\_UNIT parameter can take one of five values: ONE, ZERO, TRANSMIT\_COMPLETE, EXTEND or EXTEND\_ERROR. It represents or is equivalent to a single data bit. These values are conveyed by the signals TX\_EN, TX\_ER, TXD<7>, TXD<6>, TXD<5>, TXD<4>, TXD<3>, TXD<2>, TXD<1> and TXD<0>.

Each of the eight TXD signals conveys either a ONE or ZERO of data while TX\_EN is asserted. Eight data bit equivalents of EXTEND or EXTEND\_ERROR are conveyed by a specific encoding of the TXD<7:0> signals when TX\_EN is not asserted, and TX\_ER is asserted, see Table 35–1. Synchronization between the Reconciliation sublayer and the PHY is achieved by way of the GTX\_CLK signal. The value TRANSMIT\_COMPLETE is conveyed by the de-assertion of either TX\_EN or TX\_ER at the end of a MAC's transmission.

#### 35.2.1.1.3 When generated

The GTX\_CLK signal is generated by the Reconciliation sublayer. The TXD<7:0>, TX\_EN and TX\_ER signals are generated by the Reconciliation sublayer after every group of eight PLS\_DATA.request transactions from the MAC sublayer to request the transmission of eight data bits on the physical medium, to extend the carrier event the equivalent of eight bits, or to stop transmission.

#### 35.2.1.2 Mapping of PLS\_DATA.indicate

#### 35.2.1.2.1 Function

Map the primitive PLS\_DATA.indicate to the GMII signals RXD<7:0>, RX\_DV, RX\_ER, and RX\_CLK.

#### 35.2.1.2.2 Semantics of the service primitive

PLS DATA.indicate (INPUT UNIT)

The INPUT\_UNIT parameter can take one of three values: ONE, ZERO or EXTEND. It represents or is equivalent to a single data bit. These values are derived from the signals RX\_DV, RX\_ER, RXD<7>, RXD<6>, RXD<5>, RXD<4>, RXD<3>, RXD<2>, RXD<1>, and RXD<0>. The value of the data transferred to the MAC is controlled by GMII error indications, see 35.2.1.5.

Each of the eight RXD signals conveys either a ONE or ZERO of data while RX\_DV is asserted. Eight data bit equivalents of EXTEND are conveyed by a specific encoding of the RXD<7:0> signals when RX\_DV is not asserted, and RX\_ER is asserted; see Table 35–2. Synchronization between the Reconciliation sublayer and the PHY is achieved by way of the RX\_CLK signal.

#### 35.2.1.2.3 When generated

This primitive is generated to all MAC sublayer entities in the network after a PLS\_DATA.request is issued. Each octet transferred on RXD<7:0> will result in the generation of eight PLS\_DATA.indicate transactions.

#### 35.2.1.3 Mapping of PLS\_CARRIER.indicate

#### 35.2.1.3.1 Function

Map the primitive PLS\_CARRIER.indicate to the GMII signal CRS.

#### 35.2.1.3.2 Semantics of the service primitive

PLS\_CARRIER.indicate (CARRIER\_STATUS)

The CARRIER\_STATUS parameter can take one of two values: CARRIER\_ON or CARRIER\_OFF. CARRIER\_STATUS assumes the value CARRIER\_ON when the GMII signal CRS is asserted and assumes the value CARRIER\_OFF when CRS is de-asserted.

#### 35.2.1.3.3 When generated

The PLS\_CARRIER.indicate service primitive is generated by the Reconciliation sublayer whenever the CARRIER\_STATUS parameter changes from CARRIER\_ON to CARRIER\_OFF or vice versa.

#### 35.2.1.4 Mapping of PLS\_SIGNAL.indicate

#### 35.2.1.4.1 Function

Map the primitive PLS\_SIGNAL.indicate to the GMII signal COL.

#### 35.2.1.4.2 Semantics of the service primitive

PLS SIGNAL.indicate (SIGNAL STATUS)

The SIGNAL\_STATUS parameter can take one of two values: SIGNAL\_ERROR or NO\_SIGNAL\_ERROR. SIGNAL\_STATUS assumes the value SIGNAL\_ERROR when the GMII signal COL is asserted, and assumes the value NO\_SIGNAL\_ERROR when COL is de-asserted.

#### 35.2.1.4.3 When generated

The PLS\_SIGNAL indicate service primitive is generated whenever SIGNAL\_STATUS makes a transition from SIGNAL ERROR to NO SIGNAL ERROR or vice versa.

#### 35.2.1.5 Response to error indications from GMII

If, during frame reception, both RX\_DV and RX\_ER are asserted, the Reconciliation sublayer shall ensure that the MAC will detect a FrameCheckError in that frame.

Carrier is extended when RX\_DV is not asserted and RX\_ER is asserted with a proper encoding of RXD<7:0>. When a Carrier Extend Error is received during the extension, the Reconciliation sublayer shall send PLS\_DATA.indicate values of ONE or ZERO and ensure that the MAC will detect a FrameCheckError in the sequence.

These requirements may be met by incorporating a function in the Reconciliation sublayer that produces a received frame data sequence delivered to the MAC sublayer that is guaranteed to not yield a valid CRC result, as specified by the algorithm in 3.2.8. This data sequence may be produced by substituting data delivered to the MAC.

Other techniques may be employed to respond to Data Reception Error or Carrier Extend Error provided that the result is that the MAC sublayer behaves as though a FrameCheckError occurred in the received frame.

#### 35.2.1.6 Conditions for generation of TX\_ER

If, during the process of transmitting a frame, it is necessary to request that the PHY deliberately corrupt the contents of the frame in such a manner that a receiver will detect the corruption with the highest degree of probability, then Transmit Error Propagation shall be asserted by the appropriate encoding of TX\_ER, and TX\_EN. Similarly, if during the process of transmitting carrier extension to a frame, it is necessary to request that the PHY deliberately corrupt the contents of the carrier extension in such a manner that a receiver will detect the corruption with the highest degree of probability, then Carrier Extend Error shall be signalled by the appropriate encoding of TXD<7:0>.

This capability has additional use within a repeater. For example, a repeater that detects an RX\_ER during frame reception on an input port may propagate that error indication to its output ports by asserting TX\_ER during the process of transmitting that frame.

# 35.2.1.7 Mapping of PLS\_DATA\_VALID.indicate

#### 35.2.1.7.1 Function

Map the primitive PLS\_DATA\_VALID.indicate to the GMII signals RX\_DV, RX\_ER and RXD<7:0>.

#### 35.2.1.7.2 Semantics of the service primitive

PLS DATA VALID.indicate (DATA VALID STATUS)

The DATA\_VALID\_STATUS parameter can take one of two values: DATA\_VALID or DATA\_NOT\_VALID. DATA\_VALID\_STATUS assumes the value DATA\_VALID when the GMII signal RX\_DV is asserted, or when RX\_DV is not asserted, RX\_ER is asserted and the values of RXD<7:0> indicate Carrier Extend or Carrier Extend Error. DATA\_VALID\_STATUS assumes the value DATA\_NOT\_VALID at all other times.

#### 35.2.1.7.3 When generated

The PLS\_DATA\_VALID.indicate service primitive is generated by the Reconciliation sublayer whenever DATA\_VALID\_STATUS parameter changes from DATA\_VALID to DATA\_NOT\_VALID or vice versa.

## 35.2.2 GMII signal functional specifications

#### 35.2.2.1 GTX\_CLK (1000 Mb/s transmit clock)

GTX\_CLK is a continuous clock used for operation at 1000 Mb/s. GTX\_CLK provides the timing reference for the transfer of the TX\_EN, TX\_ER, and TXD signals from the Reconciliation sublayer to the PHY. The values of TX\_EN, TX\_ER, and TXD are sampled by the PHY on the rising edge of GTX\_CLK. GTX\_CLK is sourced by the Reconciliation sublayer.

The GTX\_CLK frequency is nominally 125 MHz, one-eighth of the transmit data rate.

#### 35.2.2.2 RX\_CLK (receive clock)

RX\_CLK is a continuous clock that provides the timing reference for the transfer of the RX\_DV, RX\_ER and RXD signals from the PHY to the Reconciliation sublayer. RX\_DV, RX\_ER and RXD are sampled by the Reconciliation sublayer on the rising edge of RX\_CLK. RX\_CLK is sourced by the PHY.

The PHY may recover the RX\_CLK from the received data or it may derive the RX\_CLK reference from a local clock (e.g., GTX\_CLK). When derived from the received data, RX\_CLK shall have a frequency equal to one-eighth of the data rate of the received signal, and when derived from a local clock a nominal frequency of 125 MHz.

When the signal received from the medium is continuous and the PHY can recover the RX\_CLK reference and supply the RX\_CLK on a continuous basis, there is no need to transition between the recovered clock reference and a local clock reference on a frame-by-frame basis. If loss of received signal from the medium causes a PHY to lose the recovered RX\_CLK reference, the PHY shall source the RX\_CLK from a local clock reference.

Transitions from local clock to recovered clock or from recovered clock to local clock shall be made only while RX\_DV and RX\_ER are de-asserted. During the interval between the assertion of CRS and the assertion of RX\_DV at the beginning of a frame, the PHY may extend a cycle of RX\_CLK by holding it in either the high or low condition until the PHY has successfully locked onto the recovered clock. Following the deassertion of RX\_DV at the end of a frame, or the de-assertion of RX\_ER at the end of carrier extension, the PHY may extend a cycle of RX\_CLK by holding it in either the high or low condition for an interval that shall not exceed twice the nominal clock period.

NOTE—This standard neither requires nor assumes a guaranteed phase relationship between the RX\_CLK and GTX\_CLK signals. See additional information in 35.4.

#### 35.2.2.3 TX\_EN (transmit enable)

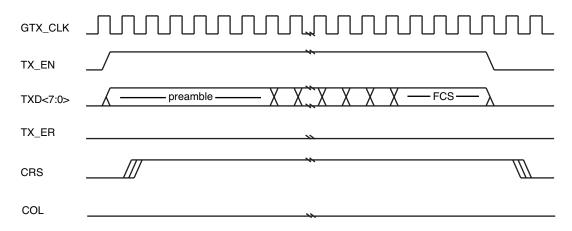

TX\_EN in combination with TX\_ER indicates the Reconciliation sublayer is presenting data on the GMII for transmission. It shall be asserted by the Reconciliation sublayer synchronously with the first octet of the preamble and shall remain asserted while all octets to be transmitted are presented to the GMII. TX\_EN shall be negated prior to the first rising edge of GTX\_CLK following the final data octet of a frame. TX\_EN is driven by the Reconciliation sublayer and shall transition synchronously with respect to the GTX\_CLK.

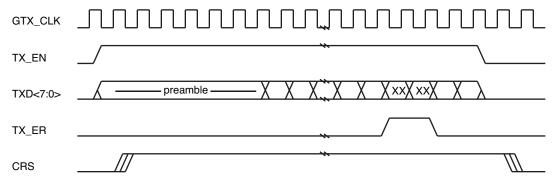

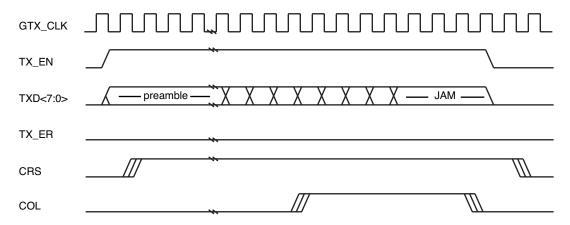

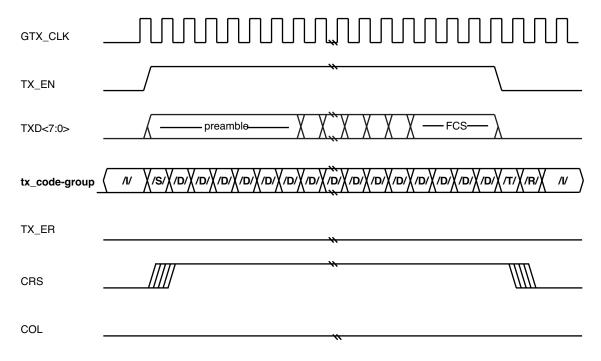

Figure 35–3 depicts TX\_EN behavior during a frame transmission with no collisions and without carrier extension or errors.

Figure 35-3 — Basic frame transmission

#### 35.2.2.4 TXD (transmit data)

TXD is a bundle of eight data signals (TXD<7:0>) that are driven by the Reconciliation sublayer. TXD<7:0> shall transition synchronously with respect to the GTX\_CLK. For each GTX\_CLK period in which TX\_EN is asserted and TX\_ER is de-asserted, data are presented on TXD<7:0> to the PHY for transmission. TXD<0> is the least significant bit. While TX\_EN and TX\_ER are both de-asserted, TXD<7:0> shall have no effect upon the PHY.

While TX\_EN is de-asserted and TX\_ER is asserted, TXD<7:0> are used to request the PHY to generate Carrier Extend or Carrier Extend Error code-groups. The use of TXD<7:0> during the transmission of a frame with carrier extension is described in 35.2.2.5. Carrier extension shall only be signalled immediately following the data portion of a frame.

Table 35–1 specifies the permissible encodings of TXD<7:0>, TX\_EN, and TX\_ER.

TX EN TX\_ER TXD<7:0> Description PLS\_DATA.request parameter Normal inter-frame TRANSMIT\_COMPLETE 0 0 00 through FF 0 1 00 through 0E Reserved 0 0F Carrier Extend 1 EXTEND (eight bits) 0 Reserved 1 10 through 1E Carrier Extend Error 0 1 1F EXTEND\_ERROR (eight bits) 0 1 20 through FF Reserved 0 00 through FF Normal data transmission ZERO, ONE (eight bits) 1 1 1 00 through FF Transmit error propagation No applicable parameter NOTE—Values in TXD<7:0> column are in hexadecimal.

Table 35–1 — Permissible encodings of TXD<7:0>, TX\_EN, and TX\_ER

#### 35.2.2.5 TX ER (transmit coding error)

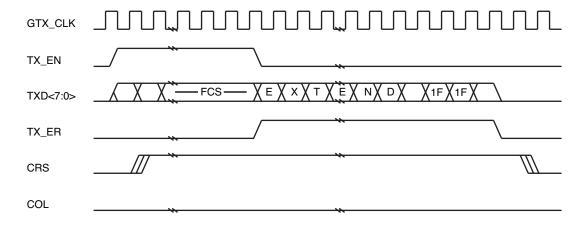

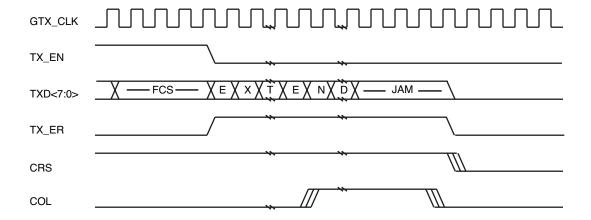

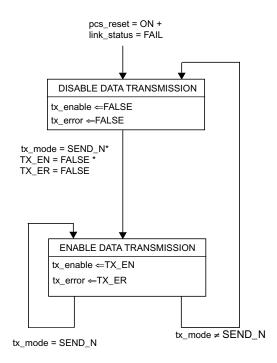

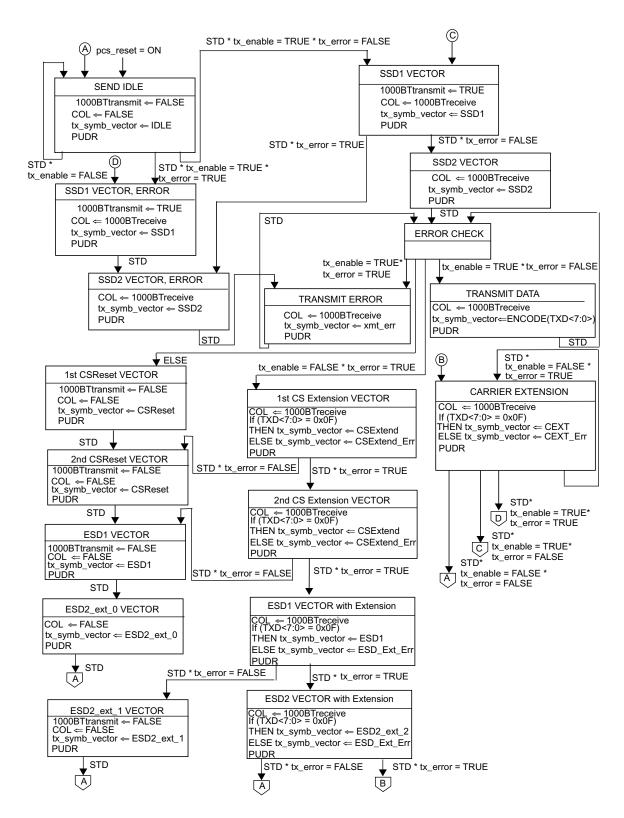

TX\_ER is driven by the Reconciliation Sublayer and shall transition synchronously with respect to the GTX\_CLK. When TX\_ER is asserted for one or more TX\_CLK periods while TX\_EN is also asserted, the PHY shall emit one or more code-groups that are not part of the valid data or delimiter set somewhere in the frame being transmitted. The relative position of the error within the frame need not be preserved. Figure 35–4 shows the behavior of TX\_ER during the transmission of a frame propagating an error.

Figure 35-4—Propagating an error within a frame

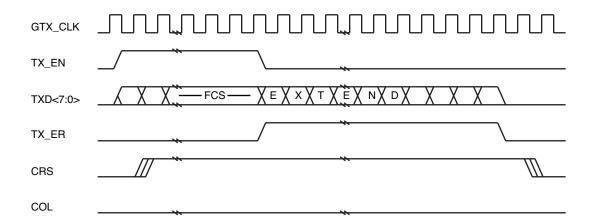

Assertion of appropriate TXD values when TX\_EN is de-asserted and TX\_ER is asserted will cause the PHY to generate either Carrier Extend or Carrier Extend Error code-groups. The transition from TX\_EN asserted and TX\_ER de-asserted to TX\_EN de-asserted and TX\_ER asserted with TXD specifying Carrier Extend shall result in the PHY transmitting an end-of-packet delimiter as the initial code-groups of the carrier extension. Figures 35–5 and 35–6 show the behavior of TX\_ER during the transmission of carrier extension. The propagation of an error in carrier extension is requested by holding TX\_EN de-asserted and TX\_ER asserted along with the appropriate value of TXD<7:0>.

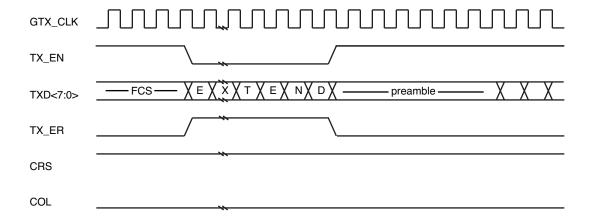

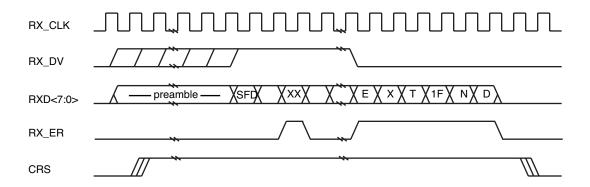

Burst transmission of frames also uses carrier extension between frames of the burst. Figure 35–7 shows the behavior of TX ER and TX EN during burst transmission.

Figure 35–5—Propagating an error within carrier extension

Figure 35-6-Transmission with carrier extension

Figure 35-7-Burst transmission

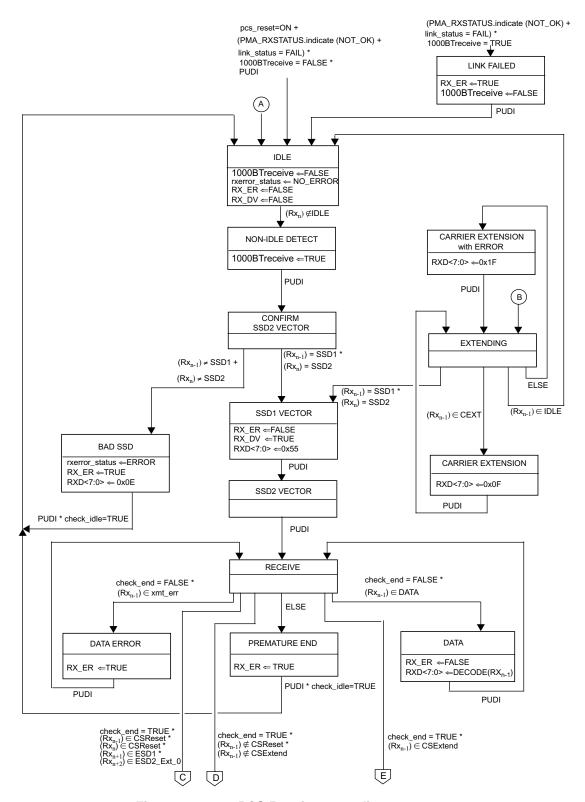

# 35.2.2.6 RX\_DV (receive data valid)

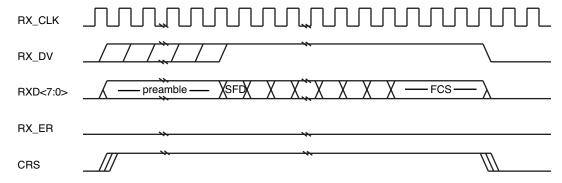

RX\_DV is driven by the PHY to indicate that the PHY is presenting recovered and decoded data on the RXD<7:0> bundle. RX\_DV shall transition synchronously with respect to the RX\_CLK. RX\_DV shall be asserted continuously from the first recovered octet of the frame through the final recovered octet and shall be negated prior to the first rising edge of RX\_CLK that follows the final octet. In order for a received frame to be correctly interpreted by the Reconciliation sublayer and the MAC sublayer, RX\_DV must encompass the frame, starting no later than the Start Frame Delimiter (SFD) and excluding any End-of-Frame delimiter.

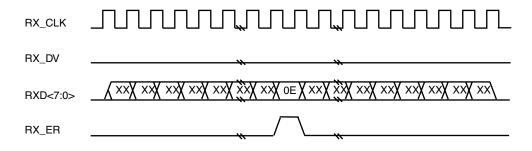

Figure 35–8 shows the behavior of RX\_DV during frame reception with no errors or carrier extension.

Figure 35-8 — Basic frame reception

#### 35.2.2.7 RXD (receive data)

RXD is a bundle of eight data signals (RXD<7:0>) that are driven by the PHY. RXD<7:0> shall transition synchronously with respect to RX\_CLK. For each RX\_CLK period in which RX\_DV is asserted, RXD<7:0> transfer eight bits of recovered data from the PHY to the Reconciliation sublayer. RXD<0> is the least significant bit. Figure 35–8 shows the behavior of RXD<7:0> during frame reception.

While RX\_DV is de-asserted, the PHY may provide a False Carrier indication by asserting the RX\_ER signal while driving the specific value listed in Table 35–2 onto RXD<7:0>. See 36.2.5.2.3 for a description of the conditions under which a PHY will provide a False Carrier indication.

In order for a frame to be correctly interpreted by the MAC sublayer, a completely formed SFD must be passed across the GMII.

In a DTE operating in half duplex mode, a PHY is not required to loop data transmitted on TXD<7:0> back to RXD<7:0> unless the loopback mode of operation is selected as defined in 22.2.4.1.2. In a DTE operating in full duplex mode, data transmitted on TXD <7:0> shall not be looped back to RXD <7:0> unless the loopback mode of operation is selected.

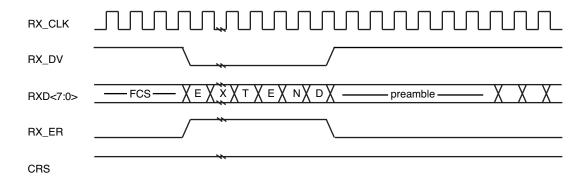

While RX\_DV is de-asserted and RX\_ER is asserted, a specific RXD<7:0> value is used to transfer recovered Carrier Extend from the PHY to the Reconciliation sublayer. A Carrier Extend Error is indicated by another specific value of RXD<7:0>. Figure 35–9 shows the behavior of RX\_DV during frame reception with carrier extension. Carrier extension shall only be signalled immediately following frame reception.

Burst transmission of frames also uses carrier extension between frames of the burst. Figure 35–10 shows the behavior of RX\_ER and RX\_DV during burst reception.

Table 35–2 specifies the permissible encoding of RXD<7:0>, RX\_ER, and RX\_DV, along with the specific indication provided by each code.

Figure 35-9—Frame reception with carrier extension

Figure 35-10-Burst reception

Table 35–2—Permissible encoding of RXD<7:0>, RX\_ER, and RX\_DV

| RX_DV  | RX_ER        | RXD<7:0>                                                  | Description              | PLS_DATA.indicate parameter |

|--------|--------------|-----------------------------------------------------------|--------------------------|-----------------------------|

| 0      | 0            | 00 through FF                                             | Normal inter-frame       | No applicable parameter     |

| 0      | 1            | 00                                                        | Normal inter-frame       | No applicable parameter     |

| 0      | 1            | 01 through 0D                                             | Reserved                 | _                           |

| 0      | 1            | 0E                                                        | False Carrier indication | No applicable parameter     |

| 0      | 1            | 0F                                                        | Carrier Extend           | EXTEND (eight bits)         |

| 0      | 1            | 10 through 1E                                             | Reserved                 | _                           |

| 0      | 1            | 1F                                                        | Carrier Extend Error     | ZERO, ONE (eight bits)      |

| 0      | 1            | 20 through FF                                             | Reserved                 | _                           |

| 1      | 0            | 00 through FF                                             | Normal data reception    | ZERO, ONE (eight bits)      |

| 1      | 1            | 00 through FF Data reception error ZERO, ONE (eight bits) |                          |                             |

| NOTE-V | alues in RXI | D<7:0> column are                                         | e in hexadecimal.        |                             |

#### 35.2.2.8 RX\_ER (receive error)

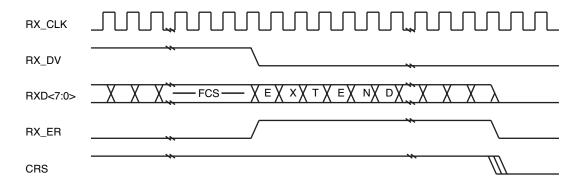

RX\_ER is driven by the PHY and shall transition synchronously with respect to RX\_CLK. When RX\_DV is asserted, RX\_ER shall be asserted for one or more RX\_CLK periods to indicate to the Reconciliation sublayer that an error (e.g., a coding error, or another error that the PHY is capable of detecting that may otherwise be undetectable at the MAC sublayer) was detected somewhere in the frame presently being transferred from the PHY to the Reconciliation sublayer.

The effect of RX\_ER on the Reconciliation sublayer is defined in 35.2.1.5. Figure 35–11 shows the behavior of RX\_ER during the reception of a frame with errors. Two independent error cases are illustrated. When RX\_DV is asserted, assertion of RX\_ER indicates an error within the data octets of a frame. An error within carrier extension is indicated by driving the appropriate value on RXD<7:0> while keeping RX\_ER asserted.

Figure 35-11 - Two examples of reception with error

Assertion of RX\_ER when RX\_DV is de-asserted with specific RXD values indicates the decode of carrier extension by the PHY. The transition from RX\_DV asserted and RX\_ER de-asserted to RX\_DV de-asserted and RX\_ER asserted with RXD specifying Carrier Extend shall result in the Reconciliation sublayer indicating EXTEND INPUT\_UNITs to the MAC. Figure 35–9 shows the behavior of RX\_DV and RX\_ER during frame reception with carrier extension.

While RX\_DV is de-asserted, the PHY may provide a False Carrier indication by asserting the RX\_ER signal for at least one cycle of the RX\_CLK while driving the appropriate value onto RXD<7:0>, as defined in Table 35–2. See 36.2.5.2.3 for a description of the conditions under which a PHY will provide a False Carrier indication. Figure 35–12 shows the behavior of RX\_ER, RX\_DV and RXD<7:0> during a False Carrier indication.

Figure 35–12—False Carrier indication

#### 35.2.2.9 CRS (carrier sense)

CRS is driven by the PHY. Except when used in a repeater, a PHY in half duplex mode shall assert CRS when either the transmit or receive medium is non-idle and shall de-assert CRS when both the transmit and receive media are idle. The PHY shall ensure that CRS remains asserted throughout the duration of a collision condition.

When used in a repeater, a PHY shall assert CRS when the receive medium is non-idle and shall de-assert CRS when the receive medium is idle.

CRS is not required to transition synchronously with respect to either the GTX\_CLK or the RX\_CLK.

The behavior of CRS is unspecified when the PHY is in full duplex mode.

Figure 35–3 and Figure 35–5 show the behavior of CRS during a frame transmission without a collision, while Figure 35–13 and Figure 35–14 show the behavior of CRS during a frame transmission with a collision.

Figure 35-13-Transmission with collision

Figure 35–14—Transmission with collision in carrier extension

#### 35.2.2.10 COL (collision detected)

COL is driven by the PHY and shall be asserted upon detection of a collision on the medium, and shall remain asserted while the collision condition persists.

COL is not required to transition synchronously with respect to either the GTX\_CLK or the RX\_CLK.

The behavior of the COL signal is unspecified when the PHY is in full duplex mode.

Figure 35–13 and Figure 35–14 show the behavior of COL during a frame transmission with a collision.

#### 35.2.2.11 MDC (management data clock)

MDC is specified in 22.2.2.11.

#### 35.2.2.12 MDIO (management data input/output)

MDIO is specified in 22.2.2.12.

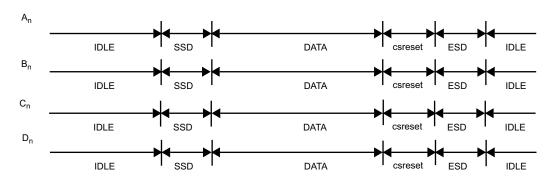

#### 35.2.3 GMII data stream

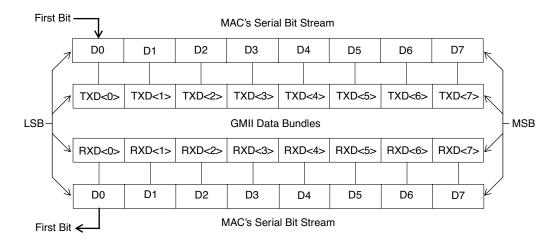

Data frames transmitted through the GMII shall be transferred within the data stream shown in Figure 35–15.

Figure 35-15-GMII data stream

For the GMII, transmission and reception of each octet of data shall be as shown in Figure 35–16.

Figure 35–16—Relationship of data bundles to MAC serial bit stream

#### 35.2.3.1 Inter-frame <inter-frame>

The inter-frame <inter-frame> period on a GMII transmit or receive path is an interval during which no data activity occurs on the path. Between bursts or single frame transmissions, the absence of data activity on the receive path is indicated by the de-assertion of both RX\_DV and RX\_ER or the de-assertion of the RX\_DV signal with an RXD<7:0> value of 00 hexadecimal. On the transmit path the absence of data activity is indicated by the de-assertion of both TX\_EN and TX\_ER.

Between frames within a burst, the inter-frame period is signalled as Carrier Extend on the GMII. As shown in Figure 35–7, this is done by asserting TX\_ER with the appropriate encoding of TXD<7:0> simultaneous with the de-assertion of TX\_EN on the transmit path; and, as shown in Figure 35–10, by asserting RX\_ER with the appropriate encoding of RXD<7:0> simultaneous with the de-assertion of RX\_DV on the receive path.

Within a burst, the MAC interFrameSpacing parameter defined in Clause 4, is measured from the de-assertion of the TX\_EN signal to the assertion of the TX\_EN signal, and between bursts measured from the de-assertion of the CRS signal to the assertion of the CRS signal.

#### 35.2.3.2 Preamble and start of frame delimiter <sfd>

#### 35.2.3.2.1 Transmit case

10101010 10101010 10101010 10101010 10101010 10101010 10101010

The SFD (Start Frame Delimiter) <sfd> indicates the start of a frame and immediately follows the preamble. The bit value of the SFD at the GMII is unchanged from that specified in 4.2.6, and is the following bit sequence:

10101011

The preamble and SFD are shown above with their bits ordered for serial transmission from left to right. As shown, the leftmost bit of each octet is the LSB of the octet and the rightmost bit of each octet is the MSB of the octet.

The preamble and SFD shall be transmitted through the GMII as octets starting from the assertion of TX\_EN.

#### 35.2.3.2.2 Receive case

The conditions for assertion of RX\_DV are defined in 35.2.2.6. The operation of 1000 Mb/s PHYs can result in shrinkage of the preamble between transmission at the source GMII and reception at the destination GMII. Table 35–3 depicts the case where no preamble bytes are conveyed across the GMII. This case may not be possible with a specific PHY, but illustrates the minimum preamble with which MAC shall be able to operate. Table 35–4 depicts the case where the entire preamble is conveyed across the GMII.

Table 35-3-Start of receive with no preamble preceding SFD

| Signal | Bit values of octets received<br>through GMH <sup>a</sup> |   |                |     |  |

|--------|-----------------------------------------------------------|---|----------------|-----|--|

| RXD0   | X                                                         | X | 1 <sup>b</sup> | D0c |  |

| RXD1   | X                                                         | X | 0              | D1  |  |

| RXD2   | X                                                         | X | 1              | D2  |  |

| RXD3   | X                                                         | X | 0              | D3  |  |

| RXD4   | X                                                         | X | 1              | D4  |  |

| RXD5   | X                                                         | X | 0              | D5  |  |

| RXD6   | X                                                         | X | 1              | D6  |  |

| RXD7   | X                                                         | X | 1              | D7  |  |

| RX_DV  | 0                                                         | 0 | 1              | 1   |  |

<sup>&</sup>lt;sup>a</sup>Leftmost octet is the first received.

Table 35-4-Start of receive with entire preamble preceding SFD

| Signal |   | Bit values of octets received through GMII <sup>a</sup> |   |   |   |   |   |   |                |                 |

|--------|---|---------------------------------------------------------|---|---|---|---|---|---|----------------|-----------------|

| RXD0   | X | 1                                                       | 1 | 1 | 1 | 1 | 1 | 1 | 1 <sup>b</sup> | D0 <sup>c</sup> |

| RXD1   | X | 0                                                       | 0 | 0 | 0 | 0 | 0 | 0 | 0              | D1              |

| RXD2   | X | 1                                                       | 1 | 1 | 1 | 1 | 1 | 1 | 1              | D2              |

| RXD3   | X | 0                                                       | 0 | 0 | 0 | 0 | 0 | 0 | 0              | D3              |

| RXD4   | X | 1                                                       | 1 | 1 | 1 | 1 | 1 | 1 | 1              | D4              |

| RXD5   | X | 0                                                       | 0 | 0 | 0 | 0 | 0 | 0 | 0              | D5              |

| RXD6   | X | 1                                                       | 1 | 1 | 1 | 1 | 1 | 1 | 1              | D6              |

| RXD7   | X | 0                                                       | 0 | 0 | 0 | 0 | 0 | 0 | 1              | D7              |

| RX_DV  | 0 | 1                                                       | 1 | 1 | 1 | 1 | 1 | 1 | 1              | 1               |

<sup>&</sup>lt;sup>a</sup>Leftmost octet is the first received.

#### 35.2.3.3 Data <data>

The data <data> in a well-formed frame shall consist of a set of data octets.

#### 35.2.3.4 End-of-Frame delimiter <efd>

De-assertion of the TX\_EN signal constitutes an End-of-Frame delimiter <efd> for data conveyed on TXD<7:0>, and de-assertion of RX\_DV constitutes an End-of-Frame delimiter for data conveyed on RXD<7:0>.

<sup>&</sup>lt;sup>b</sup>Start Frame Delimiter octet.

<sup>&</sup>lt;sup>c</sup>D0 through D7 is the first octet of the PDU (first octet of the Destination Address).

<sup>&</sup>lt;sup>b</sup>Start Frame Delimiter octet.

$<sup>^{\</sup>text{c}}\text{D0}$  through D7 is the first octet of the PDU (first octet of the Destination Address).

#### 35.2.3.5 Carrier extension <extend>

The Reconciliation sublayer signals carrier extension <extend> on the transmit path by the assertion of the TX\_ER signal with the appropriate value of TXD<7:0> simultaneous with the de-assertion of the TX\_EN signal. Carrier extension is signaled on the receive path by the assertion of the RX\_ER signal with the appropriate encoding on RXD<7:0> simultaneous with the de-assertion of RX\_DV. Carrier extension may not be present on all frames.

#### 35.2.3.6 Definition of Start of Packet and End of Packet Delimiters

For the purposes of Clause 30 layer management, the Start of Packet delimiter is defined as the rising edge of RX\_DV; and the End of Packet delimiter is defined as the falling edge of RX\_DV. (See Clause 30.2.2.2.2.)

#### 35.2.4 MAC delay constraints (with GMII)

A Gigabit Ethernet MAC with a GMII shall comply with the delay constraints in Table 35–5.

Table 35–5 – MAC delay constraints (with GMII)

| Sublayer<br>measurement<br>points | Event                                                             | Min<br>(bits) | Max<br>(bits) | Input<br>timing<br>reference | Output timing reference               |

|-----------------------------------|-------------------------------------------------------------------|---------------|---------------|------------------------------|---------------------------------------|

| MAC ⇔ GMII                        | MAC transmit start to TX_EN = 1 sampled                           |               | 48            |                              | GTX_CLK rising                        |

|                                   | CRS assert to MAC detect <sup>a</sup>                             | 0             | 48            |                              |                                       |

|                                   | CRS de-assert to MAC detect <sup>a</sup>                          | 0             | 48            |                              |                                       |

|                                   | CRS assert to TX_EN = 1 sampled (worst-case nondeferred transmit) |               | 112           |                              | GTX_CLK rising                        |

|                                   | COL assert to MAC detect                                          | 0             | 48            |                              |                                       |

|                                   | COL de-assert to MAC detect                                       | 0             | 48            |                              |                                       |

|                                   | COL assert to TXD = Jam sampled (worst-case collision response)   |               | 112           |                              | GTX_CLK rising;<br>first octet of jam |

<sup>&</sup>lt;sup>a</sup>For any given implementation: Max de-assert – Min. assert ≤ 16 bits.

#### 35.2.5 Management functions

The GMII shall use the MII management register set specified in 22.2.4. The detailed description of some management registers are dependent on the PHY type and are specified in either 28.2.4 or 37.2.5.

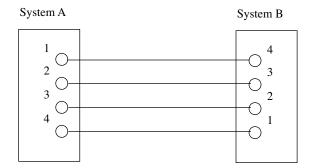

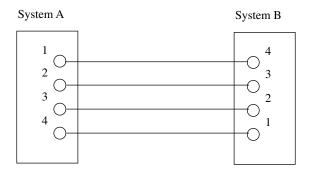

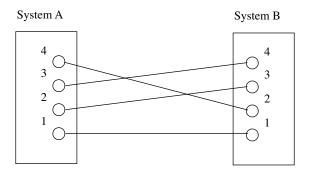

#### 35.3 Signal mapping

The GMII is specified such that implementors may share pins for implementation of the GMII, the MII specified in Clause 22 and the TBI specified in Clause 36. A recommended mapping of the signals for the GMII, MII, and TBI is shown in Table 35–6. Implementors using this recommended mapping are to comply with the GMII electrical characteristics in 35.4, MII electrical characteristics in 22.3, and the TBI electrical characteristics in 36.3 as appropriate for the implemented interfaces.

In an implementation supporting the MII and GMII, some signal pins are not used in both interfaces. For example, the TXD and RXD data bundles are four bits wide for the MII and eight bits wide for the GMII. Also, the GTX\_CLK is only used when operating as a GMII while TX\_CLK is used when operating as an MII.

Similarly, an implementation supporting both the GMII and TBI interfaces will map TBI signals onto the GMII control signal pins of TX\_ER, TX\_EN, RX\_ER, and RX\_DV. The COL and CRS signals of the GMII have no corollary in the TBI.

It is recommended that unused signal pins be driven to a valid logic state.

TBI **GMII** MII TX ER TX ER TX<9> TX EN TX\_EN TX<8> TXD<7> TX<7> TXD<6> TX<6> TXD<5> TX<5> TXD<4> TX<4> TXD<3> TXD<3> TX<3> TXD<2> TXD<2> TX<2> TXD<1> TXD<1> TX<1> TXD<0> TX<0> TXD<0> COL COL

Table 35-6-Signal mapping

| GMII   | MII    | TBI   |

|--------|--------|-------|

| RX_ER  | RX_ER  | RX<9> |

| RX_DV  | RX_DV  | RX<8> |

| RXD<7> |        | RX<7> |

| RXD<6> |        | RX<6> |

| RXD<5> |        | RX<5> |

| RXD<4> |        | RX<4> |

| RXD<3> | RXD<3> | RX<3> |

| RXD<2> | RXD<2> | RX<2> |

| RXD<1> | RXD<1> | RX<1> |

| RXD<0> | RXD<0> | RX<0> |

| CRS    | CRS    |       |

#### 35.4 Electrical characteristics

The electrical characteristics of the GMII are specified such that the GMII can be applied within a variety of 1000 Mb/s equipment types. The electrical specifications are optimized for an integrated circuit to integrated circuit application environment. This includes applications where a number of PHY integrated circuits may be connected to a single integrated circuit as may be found in a repeater. Though specified for use on a single circuit board, applications to a motherboard-to-daughterboard interconnection are not precluded.

The electrical characteristics specified in this clause apply to all GMII signals except MDIO and MDC. The electrical characteristics for MDIO and MDC are specified in 22.3.4.

#### 35.4.1 DC characteristics

All GMII drivers and receivers shall comply with the dc parametric attributes specified in Table 35–7.

The potential applied to the input of a GMII receiver may exceed the potential of the receiver's power supply (i.e., a GMII driver powered from a 3.6 V supply driving  $V_{OH}$  into a GMII receiver powered from a 2.5 V supply). Tolerance for dissimilar GMII driver and receiver supply potentials is implicit in these specifications.

#### 35.4.2 AC characteristics

The GMII ac electrical characteristics are specified in a manner that allows the implementor flexibility in selecting the GMII topologies its devices support and the techniques used to achieve the specified characteristics.

| Symbol   | Parameter           | Conditions                |                          | Min  | Max  | Units |

|----------|---------------------|---------------------------|--------------------------|------|------|-------|

| $V_{OH}$ | Output High Voltage | $I_{OH}$ = -1.0 mA        | $V_{CC} = Min$           | 2.10 | 3.60 | V     |

| $V_{OL}$ | Output Low Voltage  | $I_{OL} = 1.0 \text{ mA}$ | $V_{CC} = Min$           | GND  | 0.50 | V     |

| $V_{IH}$ | Input High Voltage  |                           |                          | 1.70 | _    | V     |

| $V_{IL}$ | Input Low Voltage   |                           |                          | _    | 0.90 | V     |

| $I_{IH}$ | Input High Current  | $V_{CC} = Max$            | $V_{IN} = 2.1 \text{ V}$ | _    | 40   | μΑ    |

| $I_{IL}$ | Input Low Current   | $V_{CC} = Max$            | $V_{IN} = 0.5 \text{ V}$ | -600 | _    | μΑ    |

Table 35-7-DC specifications

All GMII devices are required to support point-to-point links. The electrical length of the circuit board traces used to implement these links can be long enough to exhibit transmission line effects and require some form of termination. The implementor is allowed the flexibility to select the driver output characteristics and the termination technique and components to be used with its drivers for point-to-point links.

Implementors may elect to support other GMII topologies in addition to the point-to-point topology and may specify different termination techniques and components for each supported topology.

Since the output characteristics and output voltage waveforms of GMII drivers depend on the termination technique and the location of the termination components, the ac output characteristics of GMII drivers are not explicitly specified. Rather, the ac characteristics of the signal delivered to a GMII receiver are specified. These characteristics are independent of the topology and termination technique and apply uniformly to all GMII applications.

#### 35.4.2.1 Signal Timing measurements

All GMII ac timing measurements are made at the GMII receiver input and are specified relative to the  $V_{IL\_AC(max)}$  and  $V_{IH\_AC(min)}$  thresholds.

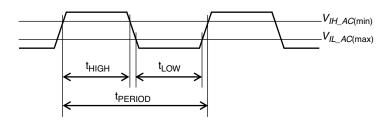

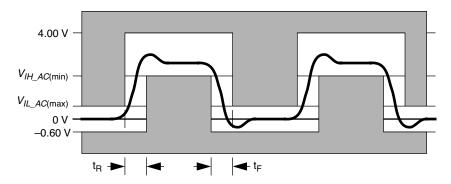

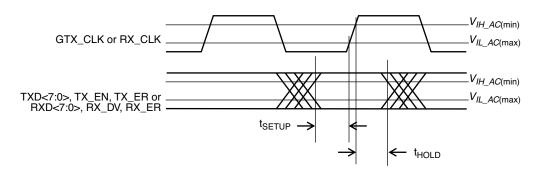

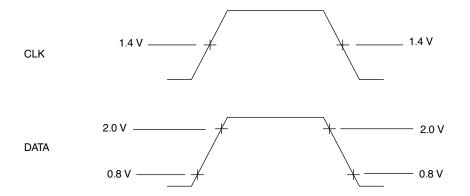

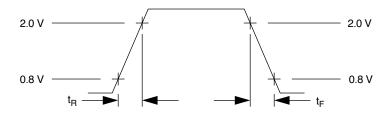

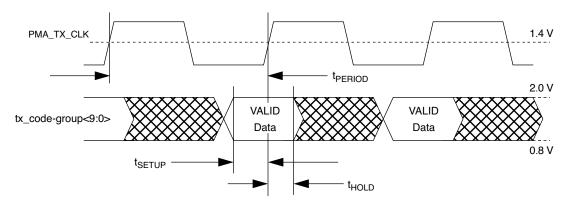

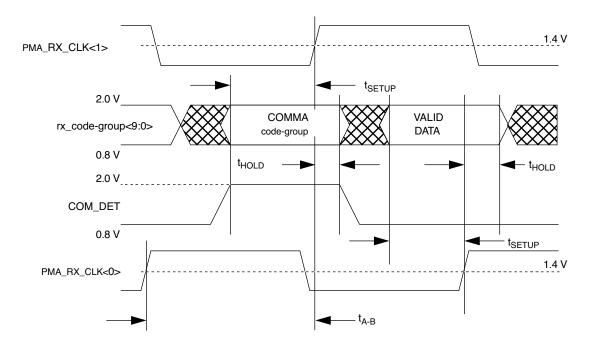

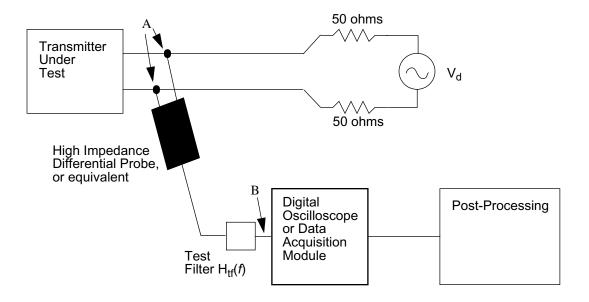

The GTX\_CLK and RX\_CLK parameters  $t_{PERIOD}$ ,  $t_{HIGH}$ , and  $t_{LOW}$  are defined in Figure 35–17. The GTX\_CLK and RX\_CLK parameters  $t_{R}$  and  $t_{F}$  and other transient performance specifications are defined in Figure 35–18. These parameters and the GTX\_CLK and RX\_CLK rising and falling slew rates are measured using the "GMII Point-to-Point Test Circuit" shown in Figure 35–20.

Figure 35-17-GTX\_CLK and RX\_CLK timing parameters at receiver input

The  $t_{SETUP}$  and  $t_{HOLD}$  parameters are defined in Figure 35–19. These parameters are measured using the "GMII Setup and Hold Time Test Circuit" shown in Figure 35–21.

NOTE-As measured at input measurement point

Figure 35-18-GMII receiver input potential template

Figure 35–19 — GMII signal timing at receiver input

Figure 35-20-GMII point-to-point test circuit

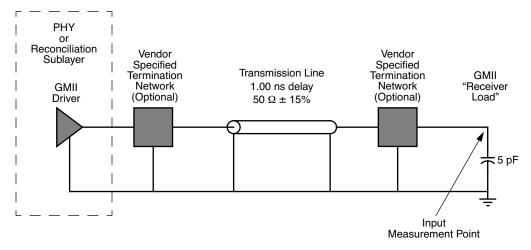

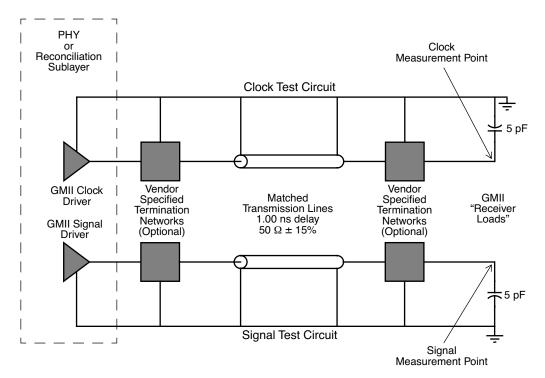

## 35.4.2.2 GMII test circuit topology

The "GMII Point-to-Point Test Circuit" is defined in Figure 35–20. All parameter measurements made with this circuit are made at the "Input Measurement Point" defined in Figure 35–20. The 5 pF capacitor is included to approximate the input load of a GMII receiver. The termination networks used to implement the "GMII Point-to-Point Test Circuit" shall be those specified by the implementor of the GMII driver for 50  $\Omega$  ± 15%

impedance transmission line point-to-point links. One or both of the termination networks specified by the implementor of the GMII driver may be straight-through connections if the networks are not needed to comply with the GMII ac and transient performance specifications.

The "GMII Point-to-Point Test Circuit" specifies a 1 ns transmission line. In a GMII implementation, the circuit board traces between the PHY and Reconciliation sublayer are not restricted to a delay of 1 ns.

The "GMII Setup and Hold Time Test Circuit" is defined in Figure 35–21. The circuit is comprised of the source of the synchronous GMII signal under test and its clock (the Reconciliation Layer or the PHY) and two "GMII Point-to-Point Test Circuits." One of the test circuits includes the GMII driver for the signal under test, the other test circuit includes the GMII driver for the clock that provides timing for the signal under test. The signal under test is measured at the "Signal Measurement Point" relative to its clock, which is measured at the "Clock Measurement Point" as defined in Figure 35–21.

Figure 35-21 - GMII setup and hold time test circuit

#### 35.4.2.3 GMII ac specifications

A GMII driver, when used in combination with the termination networks specified by the implementor of the driver for a specific GMII topology, shall produce a potential at the input pin of any GMII receiver in that topology that complies with the input potential template shown in Figure 35–18. This requirement applies for all GMII signals and any GMII topology.

To ensure that all GMII devices support point-to-point links, a GMII driver, when driving the "GMII Point-to-Point Test Circuit" shown in Figure 35–20, shall produce a potential at the "Input Measurement Point" of the "GMII Point-to-Point Test Circuit" that complies with the input potential template shown in Figure 35–18.

All GMII signal sources, including the GMII drivers, GMII receivers and GMII signals shall comply with the ac specifications in Table 35–8.

Table 35-8-AC specifications

| Symbol                       | Parameter                                                                            | Conditions                                         | Min              | Max              | Units |

|------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------|------------------|------------------|-------|

| V <sub>IL_AC</sub>           | Input Low Voltage ac                                                                 | _                                                  | _                | 0.70             | V     |

| V <sub>IH_AC</sub>           | Input High Voltage ac                                                                | -                                                  | 1.90             | _                | V     |

| f <sub>FREQ</sub>            | GTX_CLK Frequency                                                                    | -                                                  | 125 –<br>100 ppm | 125 +<br>100 ppm | MHz   |

| t <sub>PERIOD</sub>          | GTX_CLK Period                                                                       | -                                                  | 7.50             | 8.50             | ns    |

| t <sub>PERIOD</sub>          | RX_CLK Period                                                                        | -                                                  | 7.50             | _                | ns    |

| t <sub>HIGH</sub>            | GTX_CLK, RX_CLK Time High                                                            | -                                                  | 2.50             | -                | ns    |

| t <sub>LOW</sub>             | GTX_CLK, RX_CLK Time Low                                                             | -                                                  | 2.50             | -                | ns    |

| t <sub>R</sub>               | GTX_CLK, RX_CLK Rise Time                                                            | $V_{IL\_AC(\max)}$ to $V_{IH\_AC(\min)}$           | _                | 1.00             | ns    |

| t <sub>F</sub>               | GTX_CLK, RX_CLK Fall Time                                                            | $V_{IH\_AC(min)}$ to $V_{IL\_AC(max)}$             | _                | 1.00             | ns    |

| _                            | Magnitude of GTX_CLK, RX_CLK Slew Rate (rising) <sup>a</sup>                         | $V_{IL\_AC(\max)}$ to $V_{IH\_AC(\min)}$           | 0.6              | -                | V/ns  |

| _                            | Magnitude of GTX_CLK, RX_CLK Slew Rate (falling) <sup>a</sup>                        | V <sub>IH_AC(min)</sub> to V <sub>IL_AC(max)</sub> | 0.6              | _                | V/ns  |

| t <sub>SETUP</sub>           | TXD, TX_EN, TX_ER Setup to ↑ GTX_CLK and RXD, RX_DV, RX_ER Setup to ↑ RX_CLK         | -                                                  | 2.50             | -                | ns    |

| t <sub>HOLD</sub>            | TXD, TX_EN, TX_ER Hold from<br>† GTX_CLK and RXD, RX_DV,<br>RX_ER Hold from † RX_CLK | -                                                  | 0.50             | -                | ns    |

| t <sub>SETUP</sub><br>(RCVR) | TXD, TX_EN, TX_ER Setup to ↑ GTX_CLK and RXD, RX_DV, RX_ER Setup to ↑ RX_CLK         | _                                                  | 2.00             | _                | ns    |

| t <sub>HOLD</sub><br>(RCVR)  | TXD, TX_EN, TX_ER Hold from ↑ GTX_CLK and RXD, RX_DV, RX_ER Hold from ↑ RX_CLK       | -                                                  | 0.00             | _                | ns    |

<sup>&</sup>lt;sup>a</sup>Clock Skew rate is the instantaneous rate of change of the clock potential with respect to time (dV/dt), not an average value over the entire rise or fall time interval. Conformance with this specification guarantees that the clock signals will rise and fall monotonically through the switching region.

Two sets of setup and hold time parameters are specified in Table 35–8. The first set,  $t_{SETUP}$  and  $t_{HOLD}$ , applies to the source of a synchronous GMII signal and its clock and is measured using the "GMII Setup and Hold Time Test Circuit," which has transmission lines with matched propagation delays in the "clock" and "signal" paths. The second set,  $t_{SETUP(RCVR)}$  and  $t_{HOLD(RCVR)}$ , applies to the GMII receiver and specifies the minimum setup and hold times available to the GMII receiver at its input pins. The difference between the two sets of setup and hold time parameters provides margin for a small amount of mismatch in the propagation delays of the "clock" path and the "signal" paths in GMII applications.

The GMII ac specifications in Table 35–8 and the transient performance specifications in Figure 35–18 shall be met under all combination of worst-case GMII driver process and supply potential variation, ambient temperature, transmission line impedance variation, and termination network component impedance variation.

Designers of components containing GMII receivers should note that there is no upper bound specified on the magnitude of the slew rate of signals that may be applied to the input of a GMII receiver. The highfrequency energy in a high slew rate (short rise time) signal can excite the parasitic reactances of the receiver package and input pad to such a degree that the signal at the receiver input pin and the signal at the input pad differ significantly. This is particularly true for GTX\_CLK and RX\_CLK, which transition at twice the rate of other signals in the interface.

# 35.5 Protocol Implementation Conformance Statement (PICS) proforma for Clause 35, Reconciliation Sublayer (RS) and Gigabit Media Independent Interface (GMII)<sup>1</sup>

#### 35.5.1 Introduction

The supplier of a protocol implementation that is claimed to conform to Clause 35, Reconciliation Sublayer (RS) and Gigabit Media Independent Interface (GMII), shall complete the following Protocol Implementation Conformance Statement (PICS) proforma.

A detailed description of the symbols used in the PICS proforma, along with instructions for completing the PICS proforma, can be found in Clause 21.

#### 35.5.2 Identification

#### 35.5.2.1 Implementation identification

| Supplier                                                                                                                                                                      |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Contact point for enquiries about the PICS                                                                                                                                    |  |  |  |  |  |

| Implementation Name(s) and Version(s)                                                                                                                                         |  |  |  |  |  |

| Other information necessary for full identification—e.g., name(s) and version(s) for machines and/or operating systems; System Names(s)                                       |  |  |  |  |  |

| NOTE 1—Only the first three items are required for all implementations; other information may be completed as appropriate in meeting the requirements for the identification. |  |  |  |  |  |

| $NOTE\ 2-The\ terms\ Name\ and\ Version\ should\ be\ interpreted\ appropriately\ to\ correspond\ with\ a\ supplier's\ terminology\ (e.g., Type, Series, Model).$              |  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup>Copyright release for PICS proformas: Users of this standard may freely reproduce the PICS proforma in this subclause so that it can be used for its intended purpose and may further publish the completed PICS.

# 35.5.2.2 Protocol summary

| Identification of protocol standard                                                                             | IEEE Std 802.3-2002 <sup>®</sup> , Clause 35, Reconciliation Sublayer (RS) and Gigabit Media Independent Interface (GMII) |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Identification of amendments and corrigenda to this PICS proforma that have been completed as part of this PICS |                                                                                                                           |

| Have any Exception items been required? (See Clause 21; the answer Yes means that the implementation            | No [ ] Yes [ ] ation does not conform to IEEE Std 802.3-2002 <sup>®</sup> .)                                              |

| Date of Statement |  |

|-------------------|--|

|-------------------|--|

# 35.5.2.3 Major capabilities/options

| Item | Feature                                 | Subclause | Value/Comment | Status | Support           |

|------|-----------------------------------------|-----------|---------------|--------|-------------------|

| *EL  | GMII electrical interface               | 35.4      |               | О      | Yes [ ]<br>No [ ] |

| *G1  | PHY support of GMII                     | 35.1.3    |               | О      | Yes [ ]<br>No [ ] |

| G2   | Reconciliation sublayer support of GMII | 35.1.3    |               | О      | Yes [ ]<br>No [ ] |

| *HD  | Half duplex capability                  | 35.2.2.6  |               | О      | Yes [ ]<br>No [ ] |

# 35.5.3 PICS proforma tables for reconciliation sublayer and Gigabit Media Independent Interface

# 35.5.3.1 Mapping of PLS service primitives

| Item | Feature                            | Subclause | Value/Comment                                                                                              | Status | Support           |

|------|------------------------------------|-----------|------------------------------------------------------------------------------------------------------------|--------|-------------------|

| PL1  | Response to error in frame         | 35.2.1.5  | Must produce FrameCheckError when RX_DV and RX_ER are asserted                                             | M      | Yes [ ]           |

| PL2  | Response to error in extension     | 35.2.1.5  | Must produce FrameCheckEr-<br>ror on received Carrier Extend<br>Error                                      | M      | Yes [ ]           |

| PL2a | Propagation of errors in frame     | 35.2.1.6  | Assert TX_ER while TX_EN asserted                                                                          | О      | Yes [ ]           |

| PL3  | Propagation of errors in extension | 35.2.1.6  | Must send ONE or ZERO and<br>assert Carrier Extend Error to<br>propagate error within carrier<br>extension | О      | Yes [ ]<br>No [ ] |

# 35.5.3.2 GMII signal functional specifications

| Item  | Feature                                                       | Subclause | Value/Comment                                                  | Status | Support            |

|-------|---------------------------------------------------------------|-----------|----------------------------------------------------------------|--------|--------------------|

| SF1   |                                                               |           |                                                                |        |                    |

| SF2   | RX_CLK frequency                                              | 35.2.2.2  | One eighth of received data rate or nominal 125 MHz.           | M      | Yes []             |

| SF3   | RX_CLK source on loss of signal                               | 35.2.2.2  | Nominal clock reference (e.g., GTX_CLK)                        | M      | Yes []             |

| SF4   | RX_CLK transitions between recovered and nominal clock        | 35.2.2.2  | While RX_DV de-asserted                                        | M      | Yes []             |

| SF5   | RX_CLK max high/low time following de-assertion of RX_DV      | 35.2.2.2  | Maximum 2 times the nominal period                             | M      | Yes []             |

| SF6   | TX_EN assertion                                               | 35.2.2.3  | On first octet of preamble                                     | M      | Yes []             |

| SF7   | TX_EN remains asserted                                        | 35.2.2.3  | Stay asserted while all octets are transmitted over GMII       | M      | Yes []             |

| SF8   | TX_EN negation                                                | 35.2.2.3  | Before first GTX_CLK after final octet of frame                | M      | Yes []             |

| SF9   | TX_EN transitions                                             | 35.2.2.3  | Synchronous with GTX_CLK                                       | M      | Yes []             |

| SF10  | TXD <7:0> transitions                                         | 35.2.2.4  | Synchronous with GTX_CLK                                       | M      | Yes []             |

| SF11  | TXD <7:0> effect on PHY while TX_EN and TX_ER are de-asserted | 35.2.2.4  | No effect                                                      | М      | Yes []             |

| SF12  | Signalling carrier extension                                  | 35.2.2.4  | Only immediately following frame                               | M      | Yes []             |

| SF13  | TX_ER transitions                                             | 35.2.2.5  | Synchronous with GTX_CLK                                       | M      | Yes []             |

| SF14  | TX_ER effect on PHY while TX_EN is asserted                   | 35.2.2.5  | Cause PHY to emit invalid code-group                           | M      | Yes []             |

| SF15  | Transmission of end-of-packet delimiter                       | 35.2.2.5  | On de-assertion of TX_EN and simultaneous assertion of TX_ER   | M      | Yes []             |

| SF16  | TX_ER implementation                                          | 35.2.2.5  | At GMII of PHY                                                 | M      | Yes [ ]            |

| SF17  | TX_ER implementation                                          | 35.2.2.5  | Implemented if half duplex operation supported.                | HD:M   | Yes [ ]<br>N/A [ ] |

| SF18  | TX_ER driven                                                  | 35.2.2.5  | To valid state even if constant                                | M      | Yes []             |

| SF19  | RX_DV transitions                                             | 35.2.2.6  | Synchronous with RX_CLK                                        | M      | Yes []             |

| SF20  | RX_DV assertion                                               | 35.2.2.6  | From first recovered octet to final octet of a frame           | M      | Yes []             |

| SF21  | RX_DV negation                                                | 35.2.2.6  | Before the first RX_CLK following the final octet of the frame | М      | Yes []             |

| SF22  | RXD <7:0> transitions                                         | 35.2.2.7  | Synchronous with RX_CLK                                        | M      | Yes [ ]            |

| SF22a | RXD loopback                                                  | 35.2.2.7  | No loopback unless loopback mode selected                      | M      | Yes []             |

# 35.5.3.2 GMII signal functional specifications (continued)

| Item | Feature                                       | Subclause | Value/Comment                                                                   | Status | Support |

|------|-----------------------------------------------|-----------|---------------------------------------------------------------------------------|--------|---------|

| SF23 | Signalling carrier extension                  | 35.2.2.7  | Only immediately following frame                                                | M      | Yes [ ] |

| SF24 | RX_ER transitions                             | 35.2.2.8  | Synchronous with RX_CLK                                                         | M      | Yes []  |

| SF25 | RX_ER assertion                               | 35.2.2.8  | By PHY to indicate error                                                        | М      | Yes []  |

| SF26 | Generation of EXTEND                          | 35.2.2.8  | In response to simultaneous de-assertion of RX_DV and assertion of RX_ER by PHY | М      | Yes [ ] |

| SF27 | CRS assertion                                 | 35.2.2.9  | By PHY when either transmit or receive is NON-IDLE                              | M      | Yes [ ] |

| SF28 | CRS de-assertion                              | 35.2.2.9  | By PHY when both transmit and receive are IDLE                                  | M      | Yes [ ] |

| SF29 | CRS assertion during collision                | 35.2.2.9  | Remain asserted throughout                                                      | M      | Yes []  |

| SF30 | CRS assertion—repeater                        | 35.2.2.9  | By repeater when receive is NON-IDLE                                            | M      | Yes [ ] |

| SF31 | CRS de-assertion—repeater                     | 35.2.2.9  | By repeater when medium is IDLE                                                 | M      | Yes [ ] |

| SF32 | COL assertion                                 | 35.2.2.10 | By PHY upon collision on medium                                                 | M      | Yes [ ] |

| SF33 | COL remains asserted while collision persists | 35.2.2.10 |                                                                                 | M      | Yes [ ] |

# 35.5.3.3 Data stream structure

| Item | Feature                           | Subclause | Value/Comment                                   | Status | Support |

|------|-----------------------------------|-----------|-------------------------------------------------|--------|---------|

| DS1  | Format of transmitted data stream | 35.2.3    | Per Figure 35–15                                | М      | Yes [ ] |

| DS2  | Transmission order                | 35.2.3    | Per Figure 35–16                                | M      | Yes []  |

| DS3  | Preamble 7 octets long            | 35.2.3.2  | 10101010 10101010 10101010<br>10101010 10101010 | M      | Yes []  |

| DS4  | Preamble and SFD transmission     | 35.2.3.2  | Starting at assertion of TX_EN                  | М      | Yes [ ] |

| DS5  | Minimum preamble                  | 35.2.3.2  | MAC operates with minimum preamble              | M      | Yes [ ] |

| DS6  | Data length                       | 35.2.3.3  | Set of octets                                   | М      | Yes []  |

# 35.5.3.4 Delay constraints

| Item | Feature   | Subclause | Value/Comment          | Status | Support |

|------|-----------|-----------|------------------------|--------|---------|

| DC1  | MAC delay | 35.2.4    | Comply with Table 35–5 | M      | Yes []  |

# 35.5.3.5 Management functions

| Item | Feature              | Subclause | Value/Comment                          | Status | Support |

|------|----------------------|-----------|----------------------------------------|--------|---------|

| MF1  | Management registers | 35.2.5    | GMII base registers as defined in 22.4 | M      | Yes [ ] |

# 35.5.3.6 Electrical characteristics

| Item | Feature                         | Subclause | Value/Comment                                           | Status | Support            |

|------|---------------------------------|-----------|---------------------------------------------------------|--------|--------------------|

| EC1  | DC specifications               | 35.4.1    | All drivers and receivers per Table 35–7                | EL:M   | Yes [ ]<br>N/A [ ] |

| EC3  | AC and transient specifications | 35.4.2.3  | Under all combinations of worst case parameters         | EL:M   | Yes [ ]<br>N/A [ ] |

| EC4  | Topology input potential        | 35.4.2.3  | Complies with Figure 35–18 at each receiver of topology | EL:M   | Yes [ ]<br>N/A [ ] |